#### Air Force Institute of Technology

#### **AFIT Scholar**

Theses and Dissertations

Student Graduate Works

6-1998

## **Development and Packaging of Microsystems Using Foundry Services**

Jeffrey T. Butler

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Electronic Devices and Semiconductor Manufacturing Commons

#### **Recommended Citation**

Butler, Jeffrey T., "Development and Packaging of Microsystems Using Foundry Services" (1998). Theses and Dissertations. 5500.

https://scholar.afit.edu/etd/5500

This Dissertation is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact AFIT.ENWL.Repository@us.af.mil.

## DEVELPOMENT AND PACKAGING OF MICROSYSTEMS USING FOUNDRY SERVICES

Dissertation

Jeffrey T. Butler, Captain, USAF

AFIT/DS/ENG/98-08

19980629 030

Approved for public release; distribution unlimited

#### **Disclaimer**

"The views expressed in this dissertation are those of the author and do not reflect the official policy or position of the Department of Defense or the U. S. Government."

# DEVELOPMENT AND PACKAGING OF MICROSYSTEMS USING FOUNDRY SERVICES

Jeffrey T. Butler, BSEE, MSEE Captain, USAF

#### Approved:

Victor M. Bright, PhD, Committee Chairman

AFIT Department of Electrical and Computer Engineering

Paul H. Ostdiek, PhD, Lt Col, USAF, Committee Member

AFIT Department of Engineering Physics

Don S. Gelosh, PhD, Lt Col, USAF, Committee Member

AFIT Department of Electrical and Computer Engineering

John H. Comtois, PhD, Major, USAF, Committee Member

Air Force Research Laboratory, AFRL/VS

Mark E. Oxley, PhD, Dean's Representative

AFIT Department of Mathematics and Statistics

Accepted:

Robert A. Calico, Jr.

Dean, Graduate School of Engineering

#### Acknowledgments

My time at AFIT has been a learning experience beyond academics and research. It has been a journey of personal growth inspired by an increasing appreciation and trust for the love, guidance, and power of my Lord, Jesus Christ. He daily guided me through my doctoral studies and carried me every step of the way through the high points and low points. Any good thing in this dissertation is directly attributable to God's love and grace.

I am truly grateful for the love and support provided by my wonderful family. My wife, \_\_\_\_\_, has developed into a Proverbs 31 woman despite all of my bad habits and long hours away at school. \_\_\_\_\_, s first birthday was on the weekend before my first class at AFIT. Now she is a great little 'big kid' of almost four years old. I also give thanks to my Mom and Dad, \_\_\_\_\_, and \_\_\_\_\_, as well as my 'Parents In-Law', and \_\_\_\_\_\_. I also appreciate the encouragement of my brothers, \_\_\_\_\_\_, \_\_\_\_, and \_\_\_\_\_\_. I love my family dearly, and there is no doubt that I could not have been successful without your love, support, and prayers.

I also want to thank my spiritual family. The Wright-Patterson AFB Officer's Christian Fellowship and congregation of Chapel 2 have taken great care of me the past few years. I am also thankful for the AFIT Believer's Net (ABN), and the strong bonds of friendship established through this group. Thank you Jim, Frank, Jeff T., and Dan for your consistent and fervent prayers. God Bless You!

I owe a huge debt of gratitude to my advisor, Professor Victor Bright, who picked me up off the scrap heap and provided the guidance I needed to complete my dissertation at a time when I wasn't so sure everything was going to work out. Dr. Bright was the perfect advisor for me. He was enthusiastically involved with my research, and his encouragement (read: demand) to publish allowed me the opportunity to attend world-class conferences and present meaningful research results. These accomplishments would not have occurred without Dr. Bright's leadership.

I am also thankful to the other members of my research committee. Lt Col Don Gelosh was largely responsible for my coming to AFIT and has been a constant, positive influence throughout my entire stay. Lt Col Paul Ostdiek has also been a key player in my research and provided timely financial support to keep my research going. I am also genuinely grateful for having Major John Comtois on my committee. My research is built heavily upon the foundation he established at AFIT. Thanks also go to my Dean's Representative, Dr. Mark Oxley, for serving on my committee.

My sponsor, Mr. Jim Lyke of the Air Force Research Lab, provided the initial funding to get my research going. I also want to express my gratitude to Mr. Rich Saia, General Electric, for educating me on microelectronics packaging and taking a personal interest in the outcome of my dissertation research.

I also appreciate the support of many of other AFIT students. One of the reasons I joined Dr. Bright's research group was the comraderie of the students. My research was greatly enhanced by the opportunity to work with people such as: Capt. Joe Bouchard, Maj. Dave Burns, Maj. Bill Cowan, Capt. George Dalton, Capt. Glen Kading, Lt. Paul Kladitis, Capt. Rob Reid, and Capt. Paul Rounsaval. I also thank all the other guys who had a cell in Room 231 during my tenure. It was fascinating to watch the transformation of myself and other students as we progressed from taking classes to qualifying exams to research.

The support staff at AFIT also deserves praise. Charlie Powers was great at getting equipment ordered or repaired. Bill Trop and Chris O'Brien did an outstanding job supporting my work in the microfabrication lab. I also wish to thank Greg Richardson and Russ Milliron for keeping the VLSI lab going. I am also appreciative for the efforts of Angela Wilson and Carollyn Mallory in taking care of lots of paperwork and travel orders.

Finally, I must once again acknowledge the grace and mercy of Jesus Christ who brought all of these people into my life and provided everything I needed one day at a time.

- Jeffrey T. Butler

## **Table of Contents**

| Acknowledgments                                             | iii  |

|-------------------------------------------------------------|------|

| List of Figures                                             | ix   |

| List of Tables                                              | xiii |

| Abstract                                                    | xv   |

| Classical Training Insufficient                             | 1.1  |

| Chapter 1. Introduction                                     |      |

| 1.1 Research Objectives                                     |      |

| 1.1.1 Are multichip module foundries suitable for MEMS?     |      |

| 1.1.2 Modeling and Simulation of MEMS Devices and Processes |      |

| 1.1.3 Development of Microsystems Using MCMs                |      |

| 1.2 Research Accomplishments                                |      |

| 1.3 Organization of Dissertation                            | 1-6  |

| Chapter 2. Fundamentals of MEMS Fabrication                 | 21   |

| 2.1 Background                                              |      |

| 2.2 Bulk Micromachining                                     |      |

| 2.3 Surface Micromachining Processes                        |      |

| 2.4 Electroplating (LIGA)                                   |      |

| 2.5 Summary                                                 |      |

| 2.3 Summary                                                 |      |

| Chapter 3. MEMS Components and Systems                      | 3-1  |

| 3.1 Thermally Actuated Devices                              | 3-1  |

| 3.1.1 Lateral Thermal Actuator and Arrays                   | 3-2  |

| 3.1.2 Vertical Thermal Actuators                            | 3-6  |

| 3.1.3 Thermal Piston Micromirror                            |      |

| 3.2 Electrostatic Micromirrors                              | 3-9  |

| 3.2.1 Low-voltage piston mirrors                            | 3-11 |

| 3.3 Complex Systems                                         | 3-14 |

| 3.3.1 Scanning Micromirror                                  | 3-14 |

| 3.3.2 Stepper Motors                                        | 3-17 |

| 3.3.3 Flip-Up Rotating Micromirror                          |      |

| 3.4 Automated Assembly of MEMS                              | 3-20 |

| 3.4.1 Automated Assembly of Alignment Mirror                | 3-23 |

| 3.4.2 Automated Assembly of Rotating Micromirror            | 3-25 |

| 3.4.3 Use of Stressed Cantilevers for Automated Assembly    |      |

| 3.5 Summary                                                 | 3-31 |

|                                                             |      |

| Chapter 4. SPICE Modeling of Polysilicon Thermal Actuators  |      |

| 4.1 Electrothermal SPICE Models                             | 4-1  |

| 4.2 Empirical Electrothermal SPICE Model                    | 4-2  |

| 4.3 Parametric Model                                                                | 4-7        |

|-------------------------------------------------------------------------------------|------------|

| 4.3.1 Theory                                                                        | 4-8        |

| 4.3.2 Finite Element Model of Microbridge                                           | 4-10       |

| 4.3.3 Generating SPICE Subcircuits From Electrothermal Model                        | 4-17       |

| 4.3.4 Uses For Temperature Profile                                                  |            |

| 4.3.5. Limitations of the Parametric Model                                          | 4-33       |

| 4.4 Summary                                                                         | 4-34       |

| Chapter 5. MUMPs Resistivity and Fabrication Modeling                               | <i>5</i> 1 |

| 5.1 Determination of Temperature Coefficient of Resistivity for MUMPs <i>Poly 1</i> |            |

| 5.2 MUMPs Resistivity Modeling                                                      |            |

| 5.2.1 Discrepancies Between Published and Measured Resistivity Values               |            |

| 5.2.2 Resistivity As a Function of Linewidth for MUMPs                              |            |

| 5.2.3 TSUPREM Model of MUMPs Fabrication Process                                    |            |

| 5.2.4 Post Release Resistivity Effects                                              |            |

| 5.3 Polysilicon Thermal Actuator Trimming and Response                              |            |

| 5.3.1 Theoretical Model of Polysilicon Resistor Trimming                            |            |

| 5.3.2 Conformance of Polysilicon Thermal Actuators to Resistor Theory               |            |

| 5.4. Design Impacts of Polysilicon Resistance Characteristics                       |            |

| 5.5 Summary                                                                         |            |

| 5.5 Summary                                                                         | 5-51       |

| Chapter 6. Functional Integration of MEMS and CMOS                                  | 6-1        |

| 6.1 Merits of MEMS/CMOS Integration                                                 |            |

| 6.2 Voltage Amplitude Control and Implementations                                   |            |

| 6.2.1 Voltage Amplitude Control of Scanning Micromirror                             |            |

| 6.2.2 Voltage Amplitude Control of Rotating Micromirror                             |            |

| 6.3 Pulse Modulation Control for Thermal Actuators                                  |            |

| 6.3.1 Average Power Response of Thermal Actuators                                   | 6-9        |

| 6.3.2 Electrothermal SPICE Model and Pulse Modulation                               | 6-12       |

| 6.4 Pulse Modulation Control Implementations                                        | 6-15       |

| 6.4.1 Pulse Modulation Control of Scanning and Rotating Micromirror                 | 6-15       |

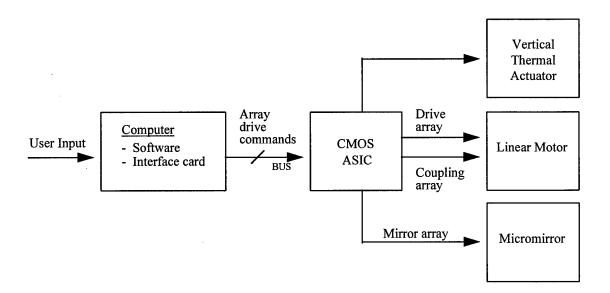

| 6.4.2 Pulse Modulation Control for Automated Assembly                               | 6-18       |

| 6.4.3 Other Applications of Pulse Modulation                                        | 6-22       |

| 6.5 Summary                                                                         | 6-26       |

| Chapter 7. Fundamentals of MEMS/MCM Packaging                                       | 7-1        |

| 7.1 MEMS and CMOS/VLSI Integration                                                  |            |

| 7.1.1 Integrated Circuit Technologies                                               |            |

| 7.1.2 MEMS and CMOS Integration Pitfalls                                            |            |

| 7.2 MCM Technologies                                                                |            |

| 7.2.1 Benefits of MCMs                                                              |            |

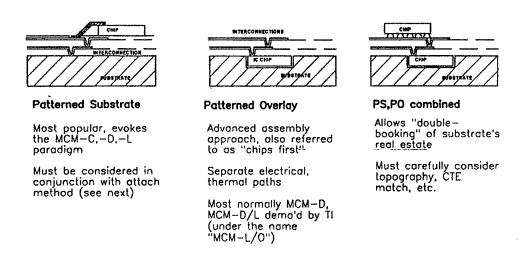

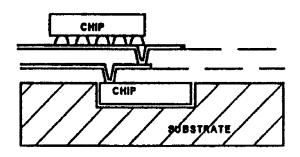

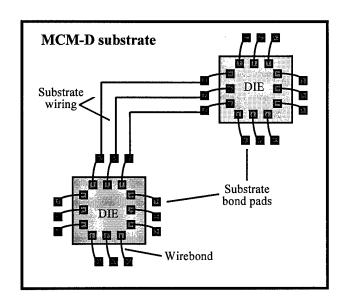

| 7.2.2 MCM Packaging Alternatives                                                    | 7-9        |

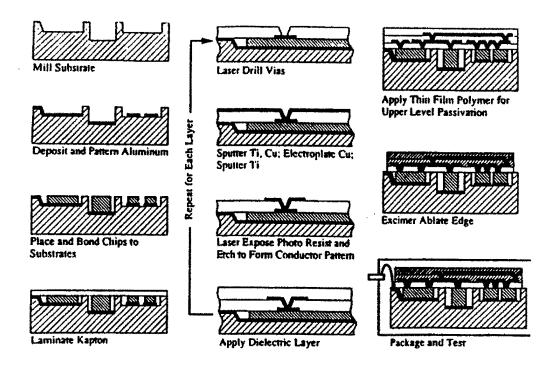

| 7.2.3 High Density Interconnect MCM Technology                                      | 7-19       |

| 7.3. MCM Future Outlook                                                 | 7-22 |

|-------------------------------------------------------------------------|------|

| 7.4 MCM Testing                                                         | 7-23 |

| 7.4.1 Parametric MCM Testing                                            | 7-24 |

| 7.4.2 Process Compliance                                                | 7-25 |

| 7.5 Summary                                                             | 7-27 |

| CI 4 O MCM DIMENSOD I '                                                 | 0.1  |

| Chapter 8. MCM-D/MEMS Packaging                                         |      |

| 8.1 Introduction                                                        |      |

| 8.2 MEMS Packaging Test Die                                             |      |

| 8.3 MCM-D/MEMS Packaging Experiments                                    |      |

| 8.4 Post Processing of MCM-D/MEMS Package                               |      |

| 8.4.1 Post Processing of Bulk Micromachined Test Die                    |      |

| 8.4.2 Post Processing of Surface Micromachined Test Die                 |      |

| 8.5 MCM-D Packaging of Pre-released MEMS                                |      |

| 8.6 Summary                                                             | 8-23 |

| Chapter 9. High Density Interconnect/MEMS Packaging                     | 0_1  |

| 9.1 Introduction                                                        |      |

| 9.2 Description of High Density Interconnect and Chip on Flex Processes |      |

| 9.2.1 High Density Interconnect                                         |      |

| 9.2.2 Chip-on-Flex                                                      |      |

| 9.3 Packaging and Post Processing of HDI and COF/MEMS Packages          |      |

| 9.3.1 Modifications to HDI/COF Process for MEMS Packaging               |      |

| 9.3.2 HDI/COF Packaging Procedure                                       |      |

| 9.4 HDI/COF Packaging of Surface Micromachined Test Die                 |      |

| 9.4.1 HDI/COF Packaging of MUMPs Die                                    |      |

| 9.4.2 HDI/COF Packaging of SUMMiT Die                                   |      |

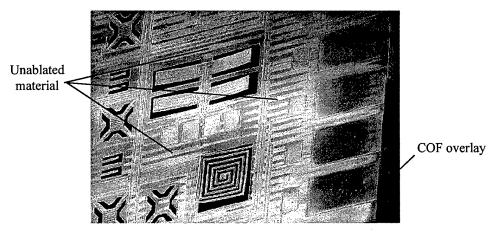

| 9.4.3 Unablated Material in Corners of Large Openings                   |      |

| 9.5 Reducing Heat Induced Damage From Laser Ablation                    |      |

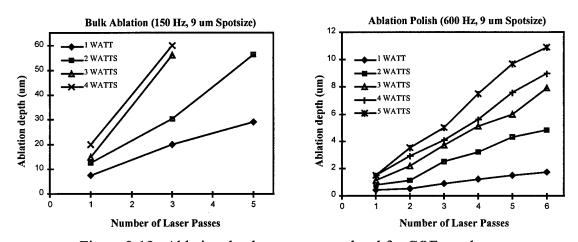

| 9.5.1 Analysis of Overlay Ablation                                      |      |

| 9.5.2 Development of Improved Overlay Ablation Procedure                |      |

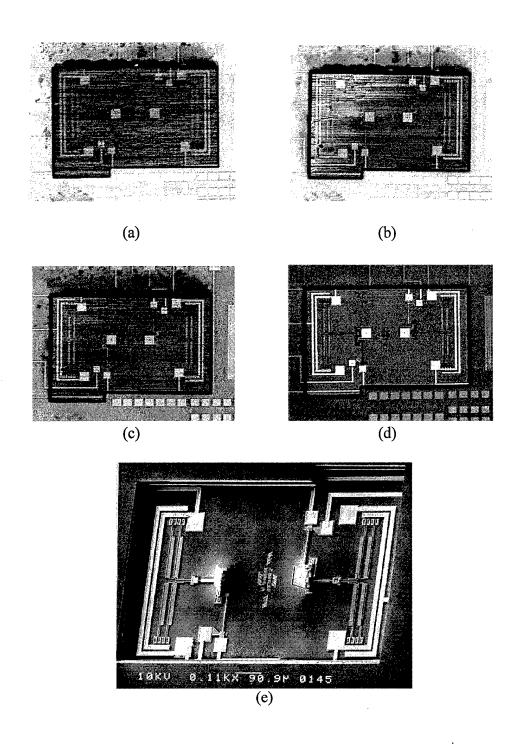

| 9.5.3 Results of Using Improved Overlay Ablation Protocol               |      |

| 9.5.4 Use of Cover Plates                                               |      |

| 9.6 Minimizing Residue In Exposed Windows With Protective Oxide Layers  |      |

| 9.6.1 Sputtered Silicon Dioxide as a Protective Layer                   |      |

| 9.6.2 Spin On Glass as a Protective Layer                               |      |

| 9.6.3 Thermal Protection of Silicon Dioxide Layers                      | 0_35 |

| 9.7 COF Packaging of Bulk Micromachined Test Die                        |      |

| 9.7.1 Packaging of Pre Released Bulk Micromachined Test Die             |      |

| 9.7.1 Packaging of Fie Released Bulk Micromachined Test Die             |      |

| 9.8 Summary                                                             |      |

|                                                                         |      |

| Chapter 10. Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10-1       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 10.1 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10-1       |

| 10.2 Resolution of Research Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-3       |

| 10.2.1 Suitability of MCM Foundries for MEMS Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-3       |

| 10.2.2 Modeling of MEMS Devices and Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10-5       |

| 10.2.3 Development of Microsystems Using MCMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10-6       |

| 10.2.3 Development of Microsystems Using MCMs  10.3 Areas for Further Research  10.3.1 MEMS Device Design and Modeling  10.3.2 Microsystem Development  10.3.3 MCM Packaging of MEMS  Appendix A. HSPICE Electrothermal Subcircuit Generator for Microbridges  A.1 Example Input File Listing  A.2 Example Output File Listing  A.3 HSPICE Electrothermal Subcircuit Generator Program Listing  Appendix B. TSUPREM Simulation of MUMPs Fabrication  B.1 TSUPREM Input File for MUMPs Poly 1 Fabrication  B.2 Final Phosphorus Doping Profiles From TSUPREM Simulation  Appendix C. VHDL Code and Descriptions for CMOS ASIC Controllers  C.1 Basic Controller | 10-7       |

| 10.3.1 MEMS Device Design and Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-7       |

| 10.3.2 Microsystem Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10-8       |

| 10.3.3 MCM Packaging of MEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10-9       |

| Appendix A. HSPICE Electrothermal Subcircuit Generator for Microbrid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | lges A-1   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| A.2 Example Output File Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A-2        |

| A.3 HSPICE Electrothermal Subcircuit Generator Program Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A-5        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

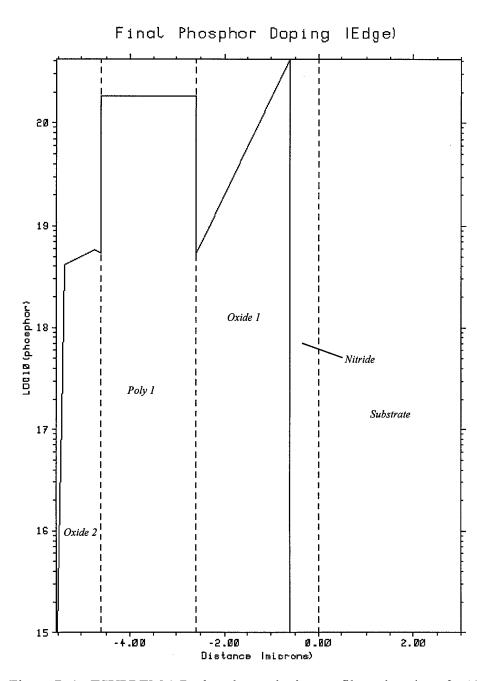

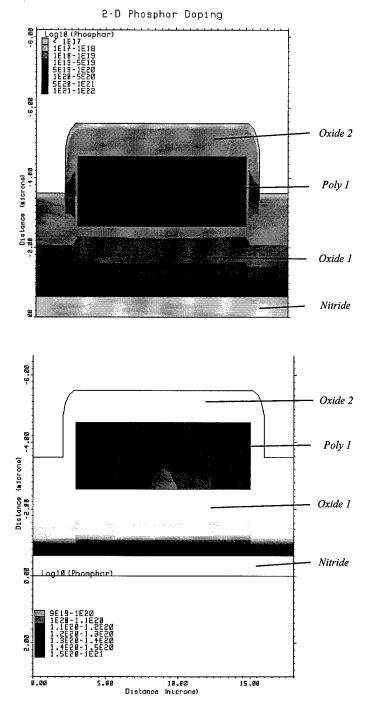

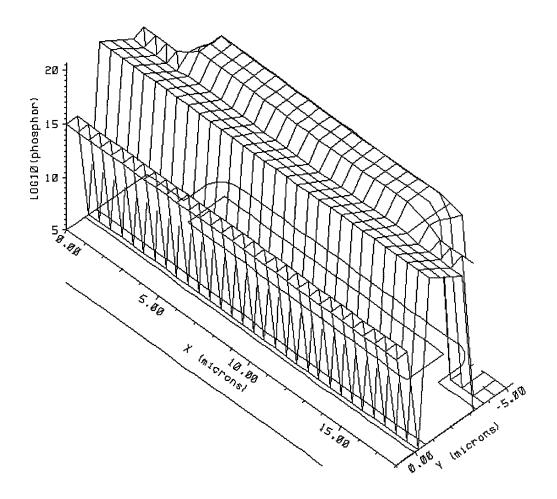

| B.2 Final Phosphorus Doping Profiles From TSUPREM Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | B-4        |

| **                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

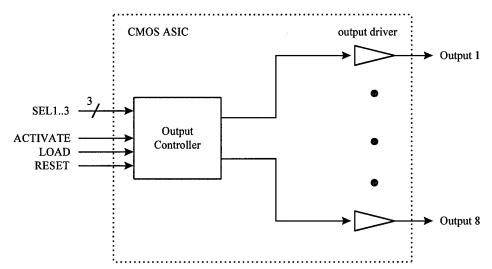

| C.1 Basic Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| C.1.1 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| C.1.2 VHDL Code Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| C.2 Pulse Modulation Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| C.2.1 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| C.2.2 Synthesized Block Diagrams and VHDL Code Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| Appendix D. Chip-on-Flex (COF)/MEMS Fabrication Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D-1        |

| Appendix E. Publications Related to This Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E-1        |

| Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BIB-1      |

| Vito                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>V</b> 1 |

## **List of Figures**

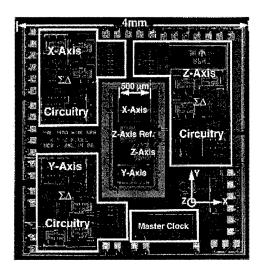

| Figure 2-1. Surface micromachined, three-axis accelerometer                     | 2-2    |

|---------------------------------------------------------------------------------|--------|

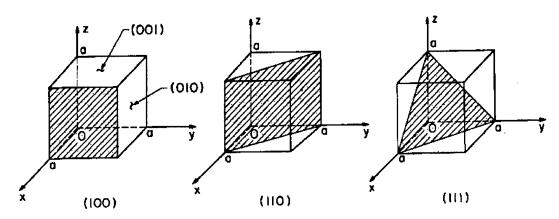

| Figure 2-2. Miller indices for primary crystal planes                           | 2-3    |

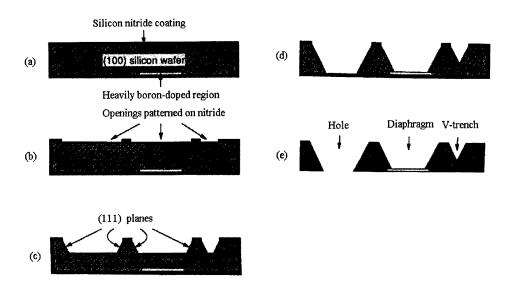

| Figure 2-3. Bulk micromachining example.                                        | 2-4    |

| Figure 2-4. Examples of devices from CMOS MEMS process                          | 2-7    |

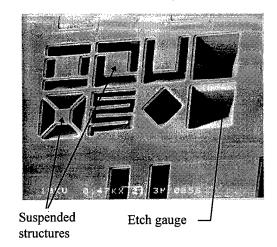

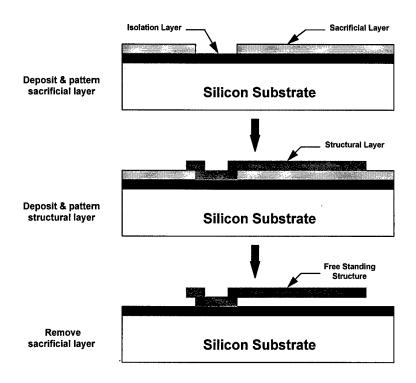

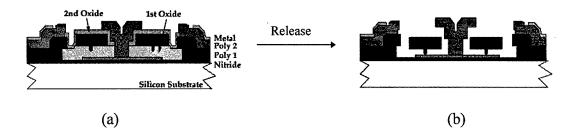

| Figure 2-5. Surface micromachining process.                                     | 2-9    |

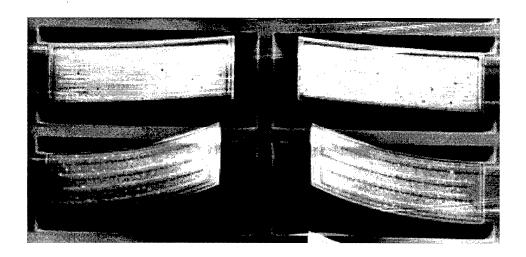

| Figure 2-6. Curling of bulk micromachined cantilevers due to residual stress    | . 2-11 |

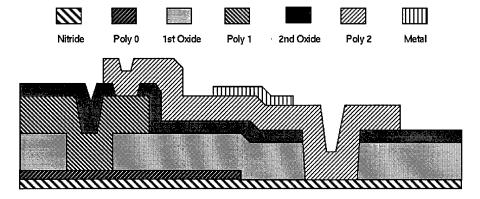

| Figure 2-7. Cross-sectional view of notional MUMPs device                       | . 2-12 |

| Figure 2-8. Side view of (a) unreleased and (b) released rotor                  | . 2-13 |

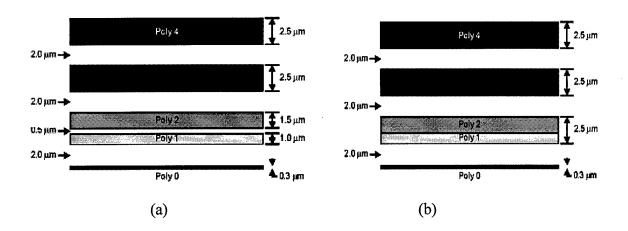

| Figure 2-9. Polysilicon Layer arrangement in Sandia SUMMiT Process              | . 2-14 |

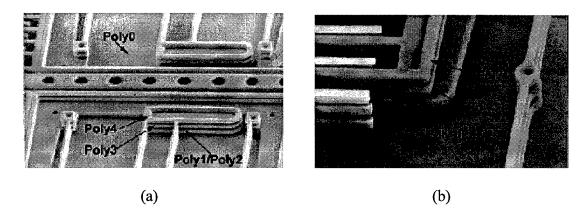

| Figure 2-10. SEM of electrostatic comb drive fabricated in the SUMMiT process   | . 2-15 |

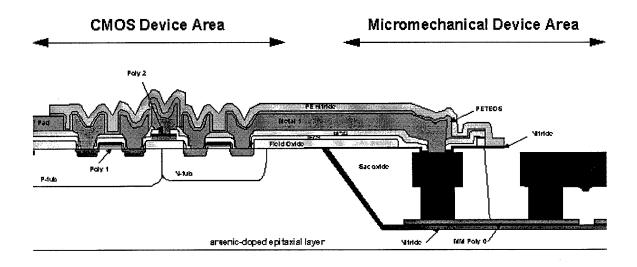

| Figure 2-11. Embedded MEMS approach to CMOS/MEMS integration                    | . 2-16 |

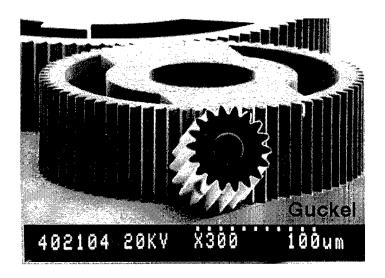

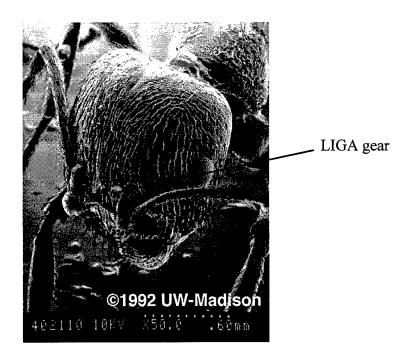

| Figure 2-12. Gears fabricated in LIGA process at University of Wisconsin        | . 2-17 |

| Figure 2-13. Micrograph of 100 µm diameter LIGA gear on the head of an ant      | . 2-19 |

|                                                                                 |        |

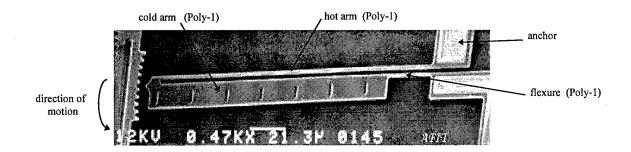

| Figure 3-1. Basic design of the lateral thermal actuator                        |        |

| Figure 3-2. Original actuator array design.                                     |        |

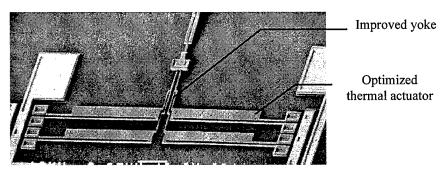

| Figure 3-3. Improved actuator array using new yoke                              | 3-5    |

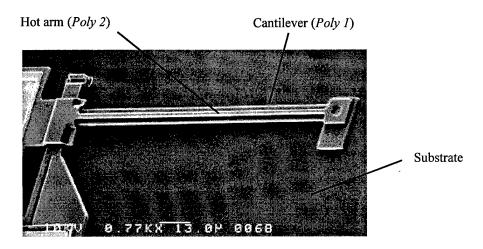

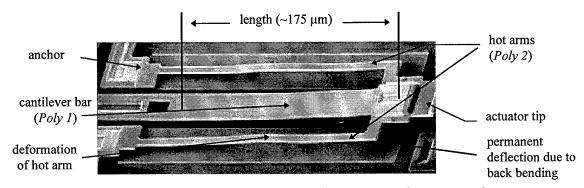

| Figure 3-4. Vertical thermal actuator                                           | 3-6    |

| Figure 3-5. A double hot arm vertical thermal actuator                          | 3-7    |

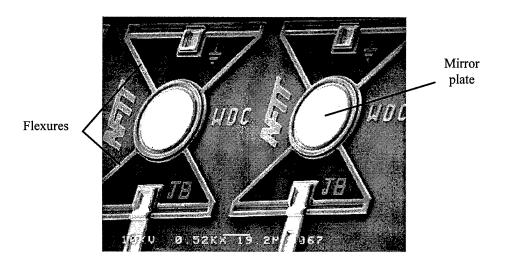

| Figure 3-6. Thermal piston micromirrors                                         |        |

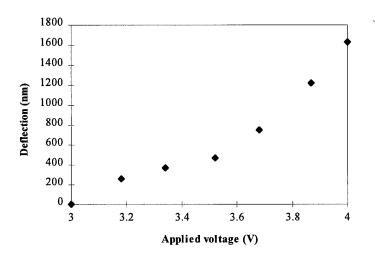

| Figure 3-7. Deflection versus voltage for thermal piston micromirror            | 3-9    |

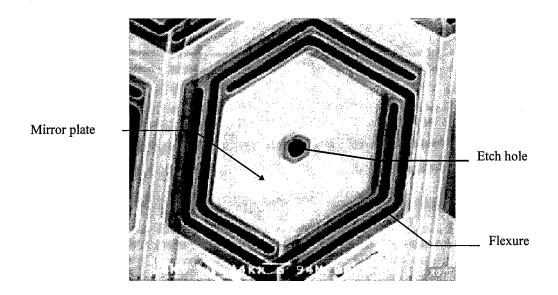

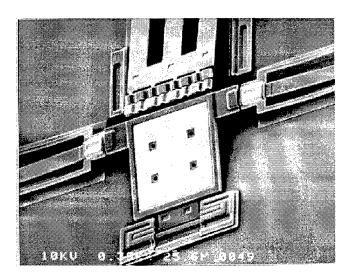

| Figure 3-8. Scanning electron micrograph (SEM) of hexagonal micromirror         | . 3-10 |

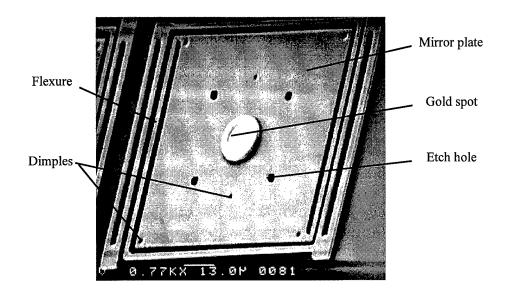

| Figure 3-9. Low-voltage micromirror                                             |        |

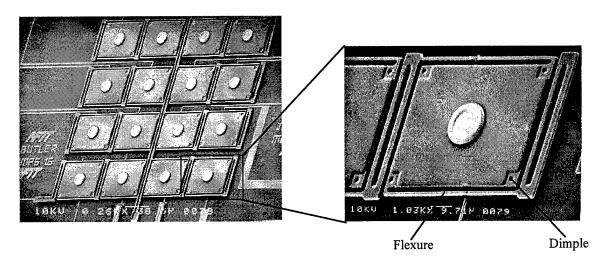

| Figure 3-10. Improved low voltage mirror design                                 | . 3-13 |

| Figure 3-11. Scanning micromirror system.                                       |        |

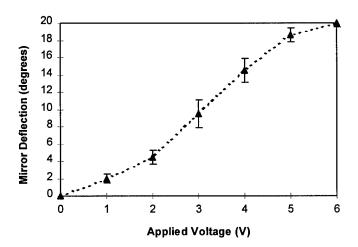

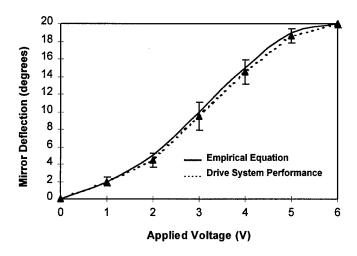

| Figure 3-12. Mirror deflection versus applied voltage for scanning micromirror  | . 3-16 |

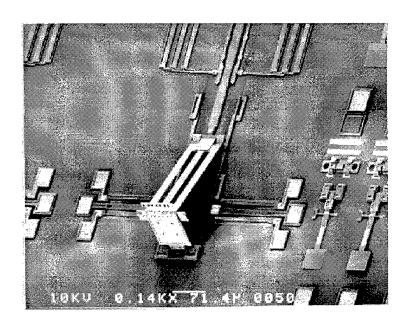

| Figure 3-13. Stepper motor geared to linear bar.                                | . 3-18 |

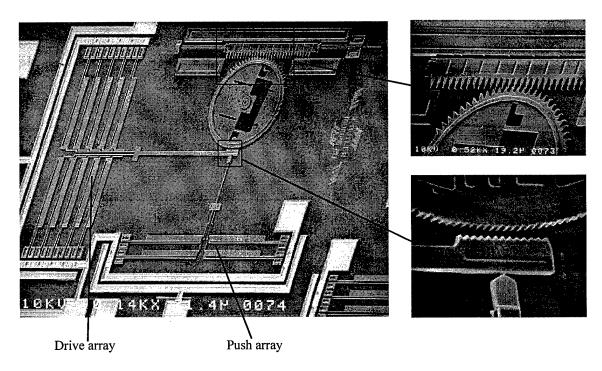

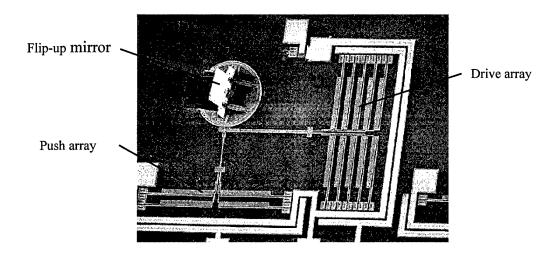

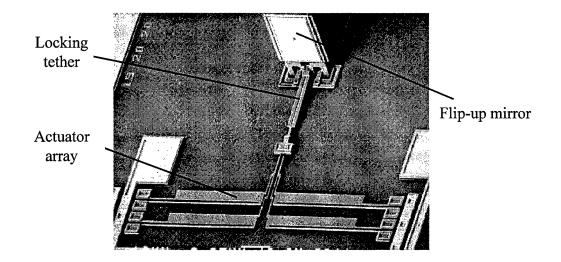

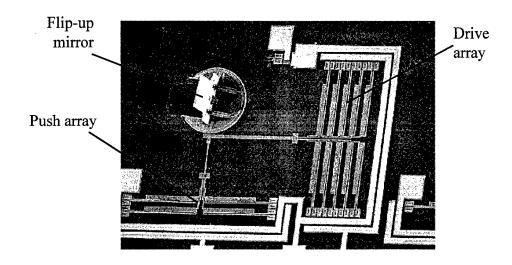

| Figure 3-14. Flip-up, rotating micromirror system.                              | . 3-19 |

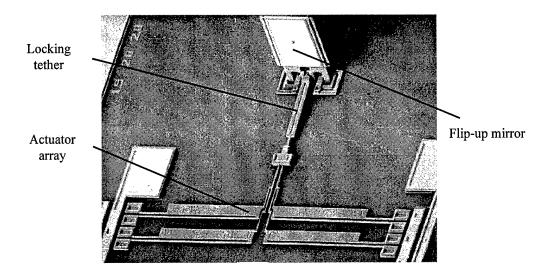

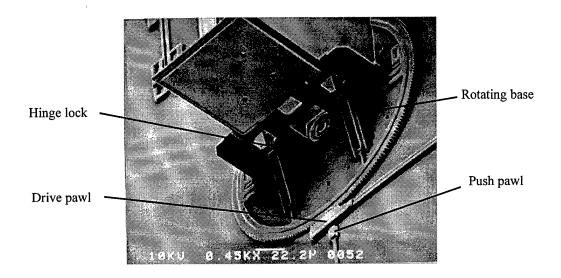

| Figure 3-15. Close-up view of rotating base and flip-up mirror                  | . 3-20 |

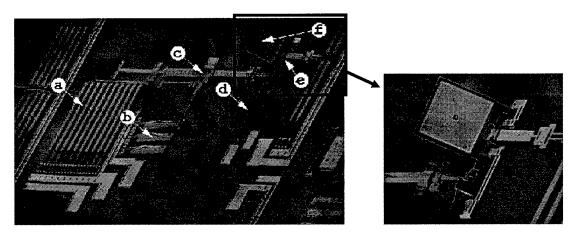

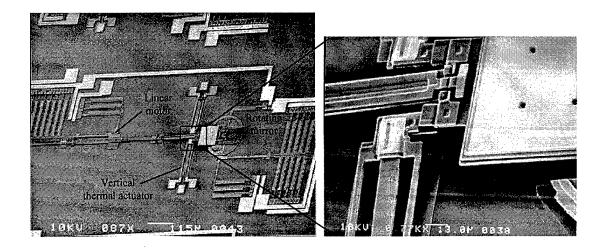

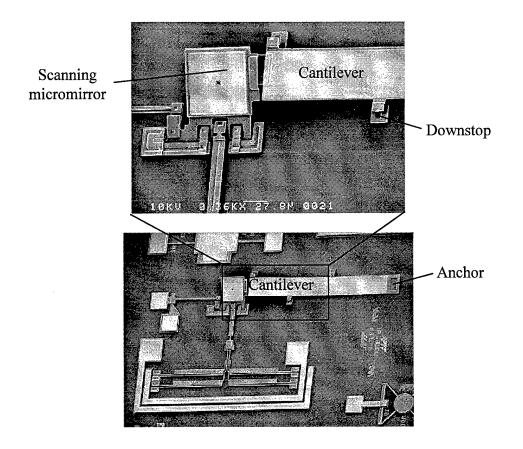

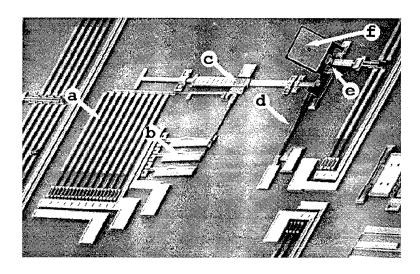

| Figure 3-16. An automated assembly system connected to a scanning micromirror   |        |

| Figure 3-17. A small polysilicon plate is extended from the base of micromirror |        |

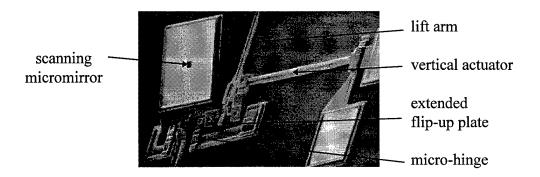

| Figure 3-18. Automated assembly system attached to an alignment mirror          |        |

| Figure 3-19. Alignment mirror lifted off the substrate                          |        |

| Figure 3-20. Alignment mirror after assembly.                                   |        |

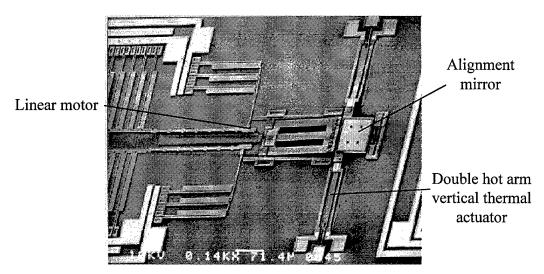

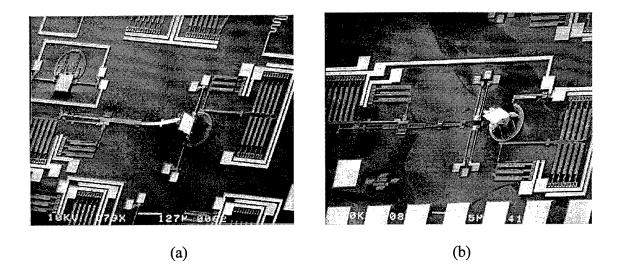

| Figure 3-21. Automated assembly system attached to rotating micromirror         | . 3-26 |

| Figure 3-22. Rotating micromirror (a) during and (b) after assembly             |        |

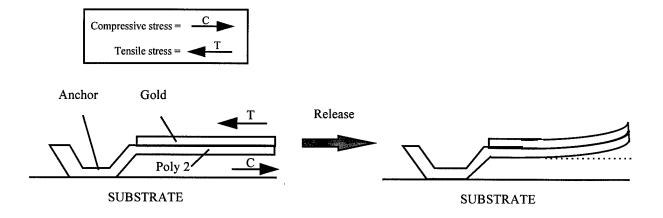

| Figure 3-23. Example of cantilever curling due to residual material stress      |        |

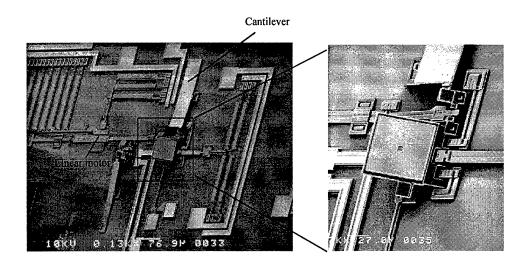

| Figure 3-24. Stressed cantilever used to lift scanning micromirror              |        |

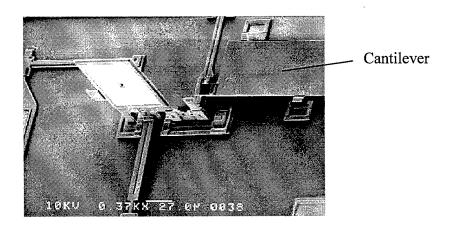

| Figure 3-25. Scanning micromirror lifted into locked position by cantilever     |        |

| Figure 3-26. Stressed cantilever used as part of the mirror assembly system     | . 3-30 |

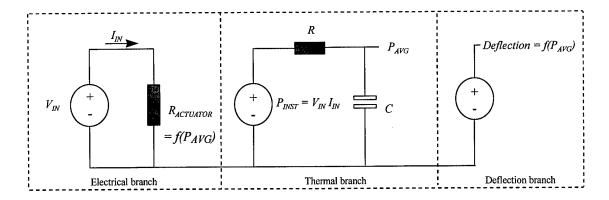

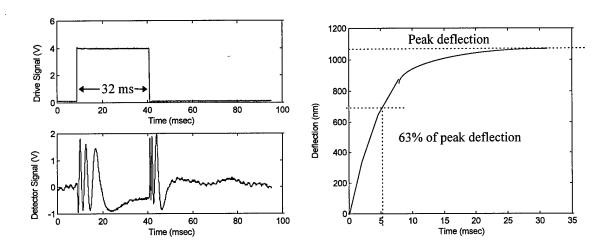

| Figure 4-1. Schematic of empirical electrothermal model for thermal actuator                       |        |

|----------------------------------------------------------------------------------------------------|--------|

| Figure 4-2. Raw drive signal and detector signal from laser interferometer                         | 4-4    |

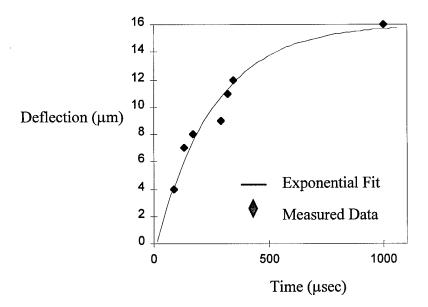

| Figure 4-3. Exponential curve fit of measured transient response of lateral actuator               | 4-5    |

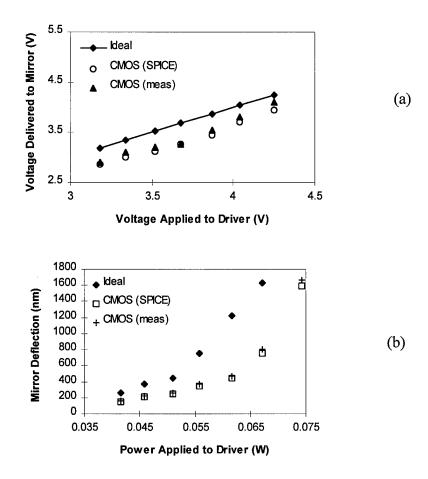

| Figure 4-4. (a) Driver output loading and (b) deflection for micromirror                           | 4-7    |

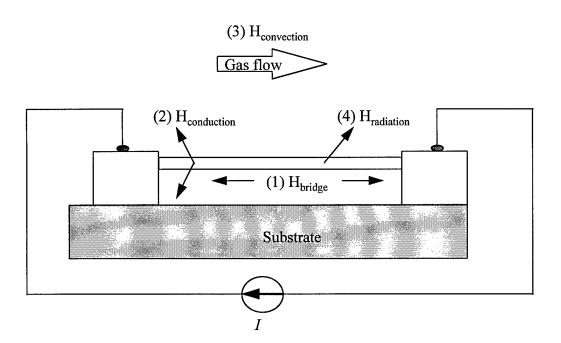

| Figure 4-5. Heat loss mechanisms in polysilicon microbridge                                        | 4-9    |

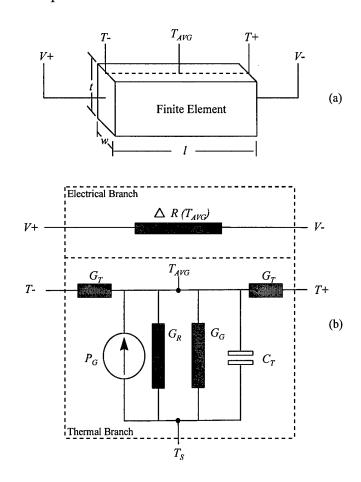

| Figure 4-6. (a) Physical and (b) electrothermal representation of finite element                   | . 4-11 |

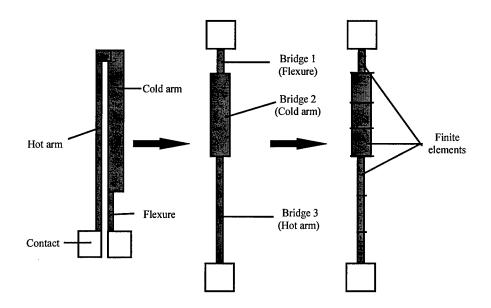

| Figure 4-7. Lateral thermal actuator as a series of three microbridges                             | . 4-18 |

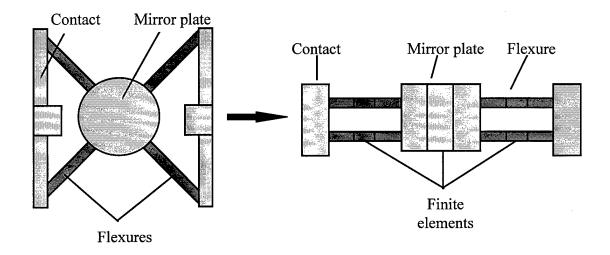

| Figure 4-8. Decomposition of thermal piston micromirror for model representation.                  | . 4-19 |

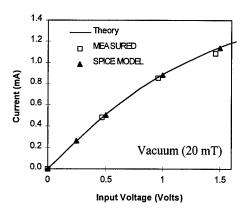

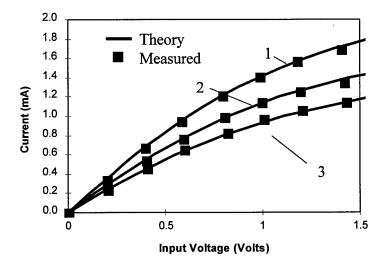

| Figure 4-9. Theoretical, SPICE model, and measured current versus voltage                          | . 4-21 |

| Figure 4-10. Measured and SPICE model current vs. voltage for thermal mirror                       | . 4-21 |

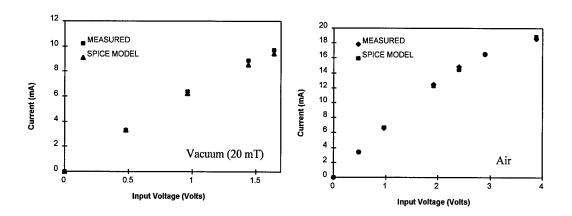

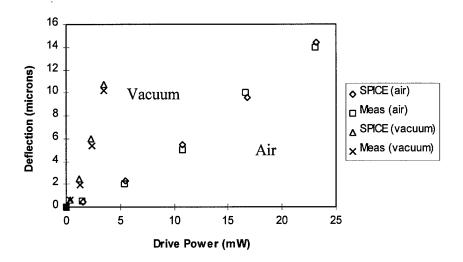

| Figure 4-11. SPICE model and measured deflection versus average power                              | . 4-23 |

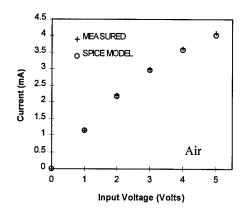

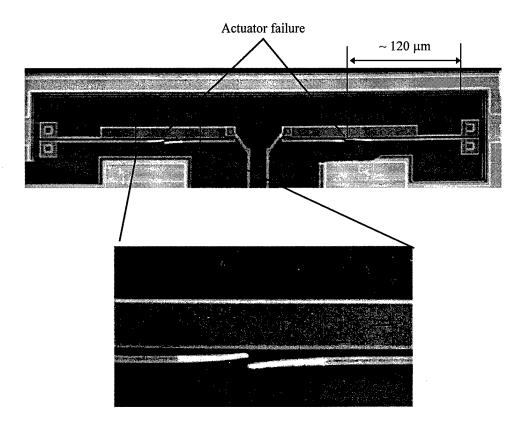

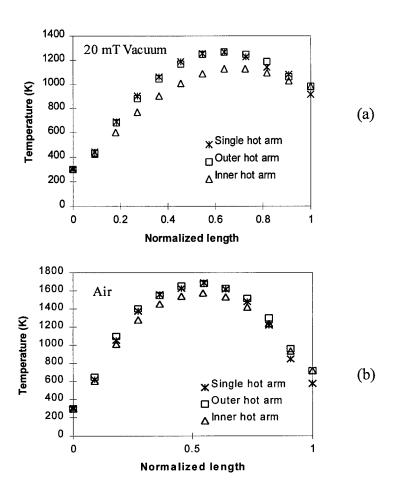

| Figure 4-12. Two element actuator array driven to failure 20 mT vacuum                             | . 4-25 |

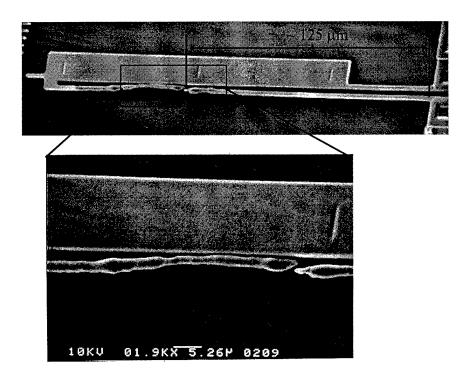

| Figure 4-13. Lateral thermal actuator driven to failure in air                                     | . 4-26 |

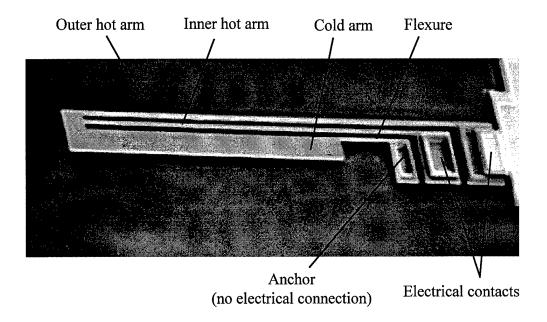

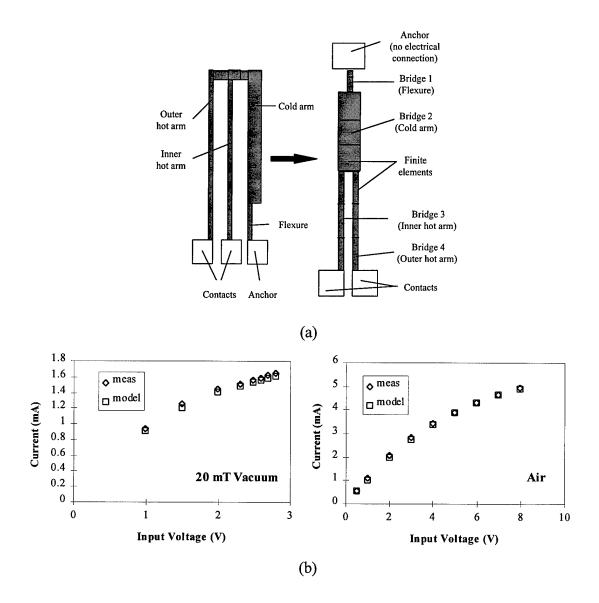

| Figure 4-14. Double hot arm thermal actuator                                                       | . 4-28 |

| Figure 4-15. SPICE and measured deflection versus average power for double arm                     | . 4-29 |

| Figure 4-16. Comparison of SPICE model hot arm temperature profiles                                | . 4-32 |

|                                                                                                    |        |

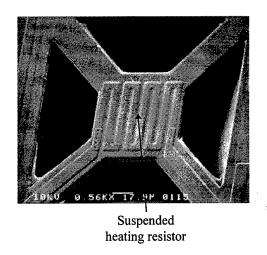

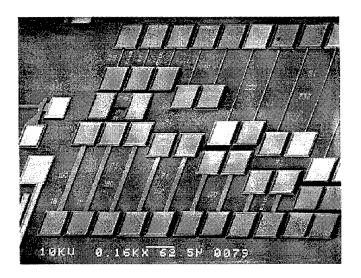

| Figure 5-1. Microbridge array used for determination of Poly 1 TCR                                 | 5-3    |

| Figure 5-2. Measured versus calculated I-V characteristics for microbridges                        | 5-4    |

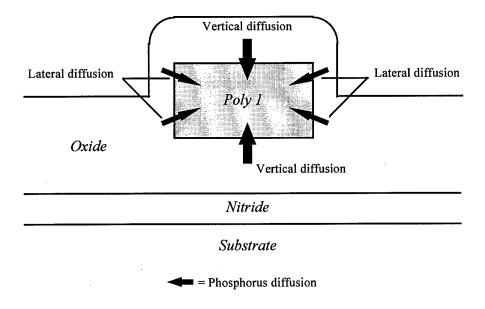

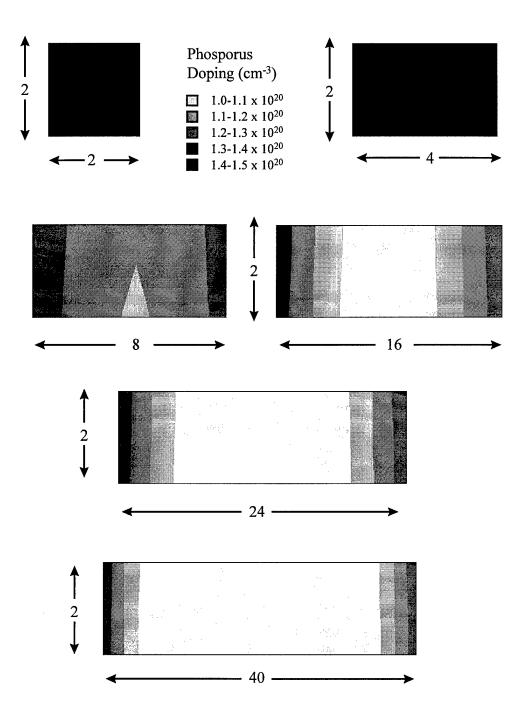

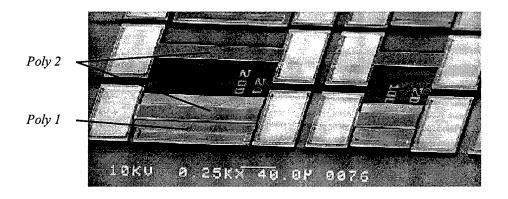

| Figure 5-3. Lateral diffusion in MUMPs Poly 1                                                      | 5-7    |

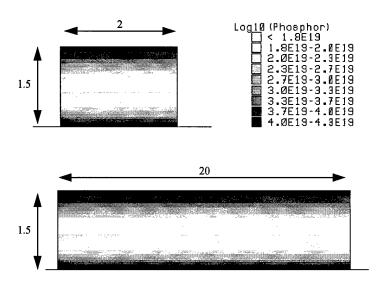

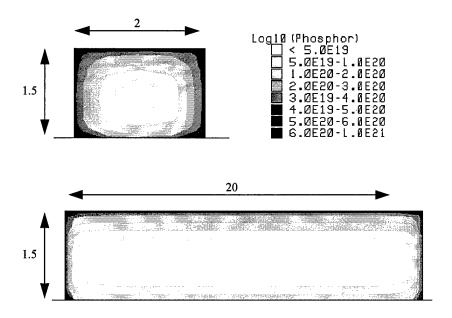

| Figure 5-4. TSUPREM cross-section view of phosphorus doping profile of Poly 1                      | . 5-10 |

| Figure 5-5. TSUPREM cross-section view of phosphorus doping profile of Poly 2                      | . 5-12 |

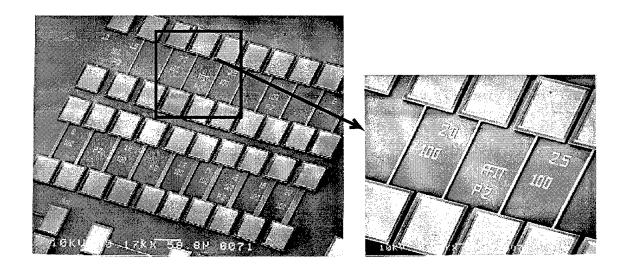

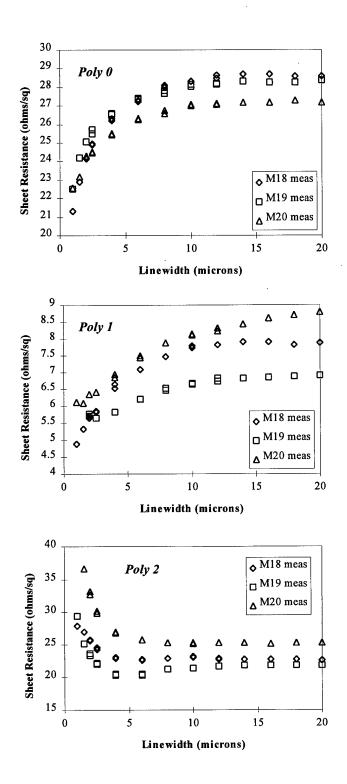

| Figure 5-6. Poly 2 test bridge array used for validating TSUPREM model                             | . 5-12 |

| Figure 5-7. Measured variation in MUMPs polysilicon sheet resistance, Rs                           | . 5-13 |

| Figure 5-8. Poly 2 bridge and Poly 2 bridge with underlying Poly 1                                 | . 5-16 |

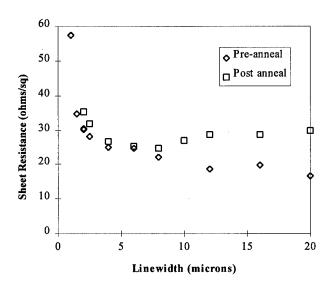

| Figure 5-9. Comparison of pre and post anneal sheet resistance for Poly 2                          | . 5-17 |

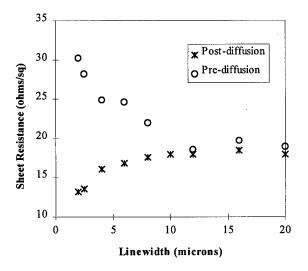

| Figure 5-10. Comparison of pre and post diffusion sheet resistance for Poly 2                      | . 5-18 |

| Figure 5-11. TSUPREM cross-section of Poly 2 test bridge after diffusion                           | . 5-19 |

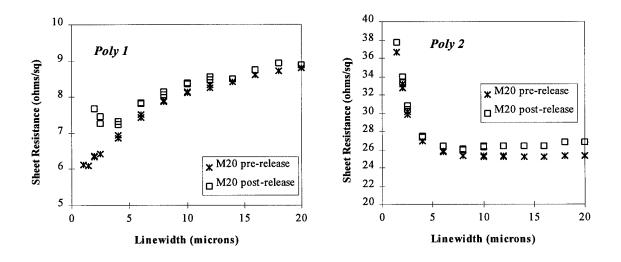

| Figure 5-12. Comparison of pre and post release R <sub>s</sub> for <i>Poly 1</i> and <i>Poly 2</i> | . 5-20 |

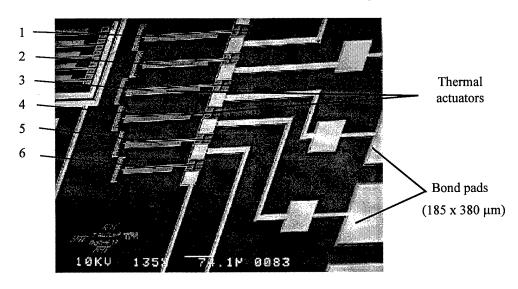

| Figure 5-13. Array of lateral actuators used for measuring electrochemical etch                    | . 5-22 |

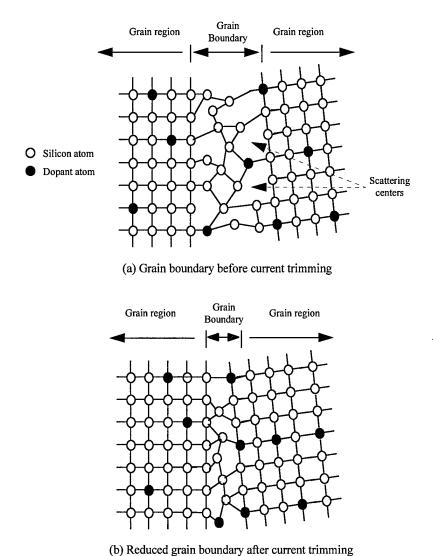

| Figure 5-14. Pictorial representation of polysilicon grain boundary                                |        |

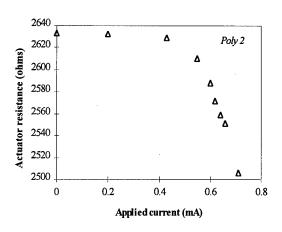

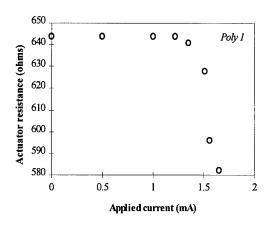

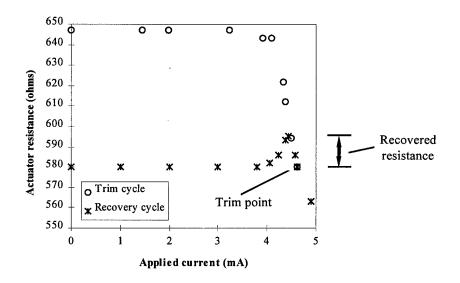

| Figure 5-15. Poly 1 and Poly 2 lateral thermal actuator resistance trimming                        | . 5-28 |

| Figure 5-16. Recovery characteristics of polysilicon actuator operated in air                      | . 5-28 |

|                                                                                                    |        |

| Figure 6-1. Scanning micromirror system.                                                           |        |

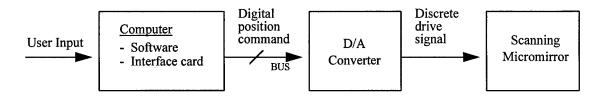

| Figure 6-2. Scanning micromirror and block diagram of position control system                      |        |

| Figure 6-3. Mirror deflection versus applied voltage for scanning micromirror                      |        |

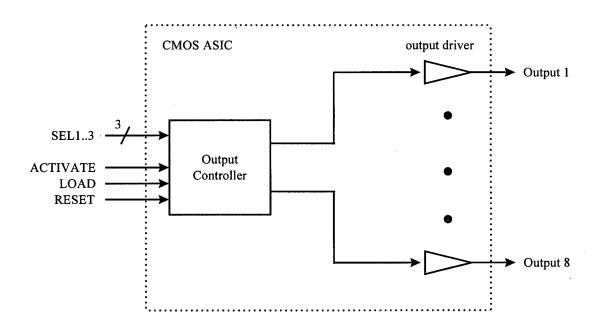

| Figure 6-4. Block diagram of CMOS ASIC.                                                            |        |

| Figure 6-5. Rotating micromirror system.                                                           |        |

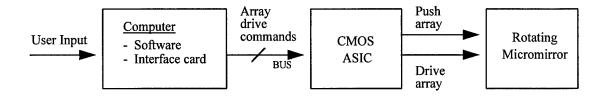

| Figure 6-6. Rotating micromirror and block diagram of the position control system.                 |        |

| Figure 6-7. Average power required for 8 µm deflection of lateral actuator                         |        |

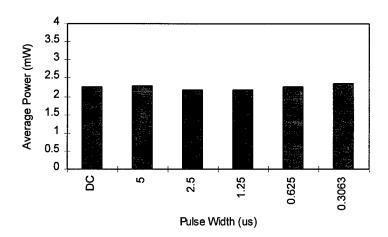

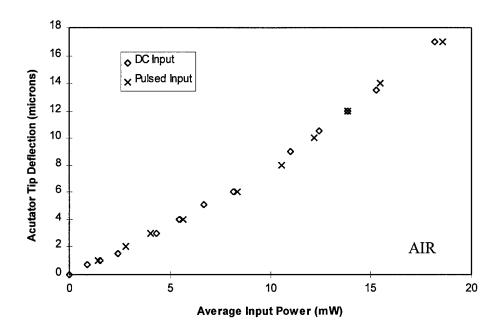

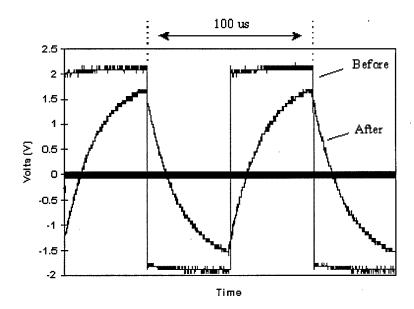

| Figure 6-8. Deflection versus average power for a thermal actuator                                 | . 6-11 |

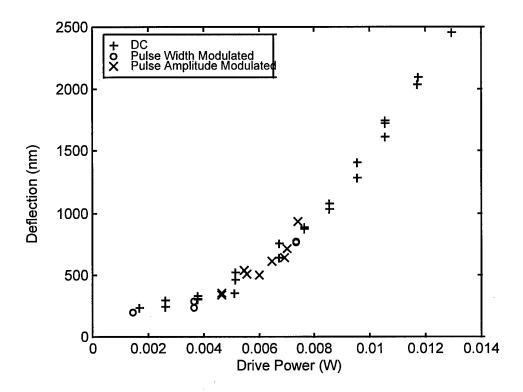

| Figure 6-9. Deflection vs. power for a thermal piston micromirror               | 6-13 |

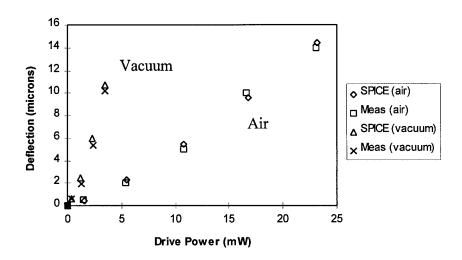

|---------------------------------------------------------------------------------|------|

| Figure 6-10. SPICE model and measured deflection versus average power           | 6-14 |

| Figure 6-11. Block diagram of CMOS ASIC.                                        | 6-16 |

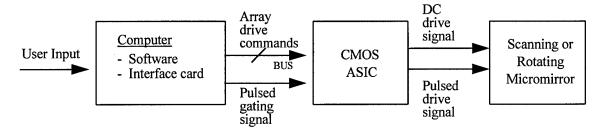

| Figure 6-12. Micromirror position control system using pulse width modulation   | 6-18 |

| Figure 6-13. Automated assembly system for scanning micromirror                 | 6-19 |

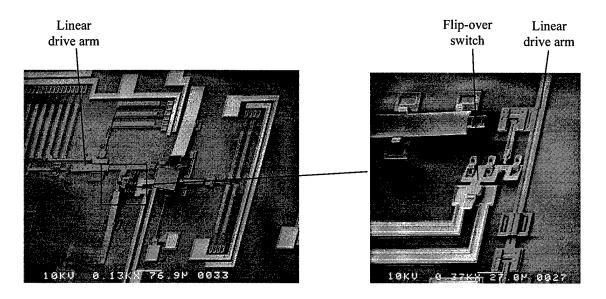

| Figure 6-14. Computer based control system for automated assembly               | 6-20 |

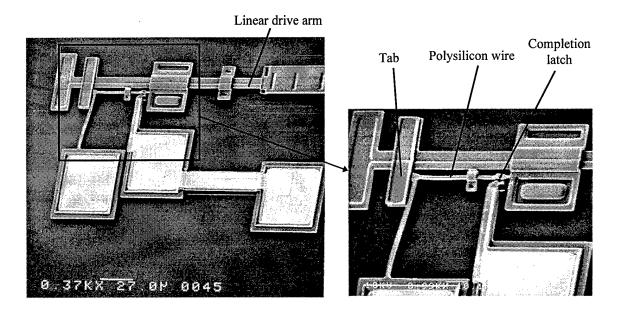

| Figure 6-15. Polysilicon switch for detecting completion of automated assembly  | 6-21 |

| Figure 6-16. Gold flip-over switch incorporated into automated assembly system  | 6-22 |

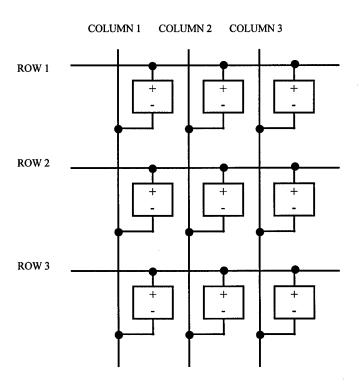

| Figure 6-17. 3 x 3 array of devices using row, column addressing                | 6-23 |

| Figure 6-18. Resistive and capacitive impact of a long <i>Poly 0</i> wire       | 6-25 |

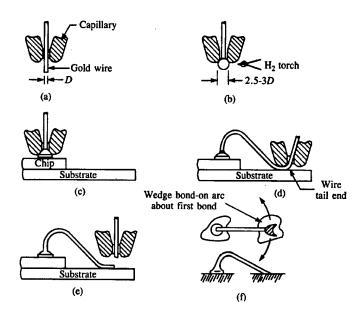

| Figure 7-1. Processing steps for thermosonic bonding of a gold wire             |      |

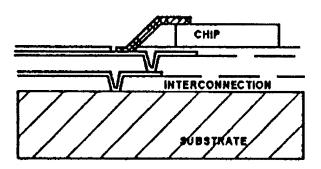

| Figure 7-2. An example of tab interconnect on an MCM-D substrate                | 7-16 |

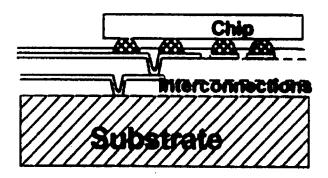

| Figure 7-3. An example of flip chip interconnect on an MCM-D substrate          | 7-17 |

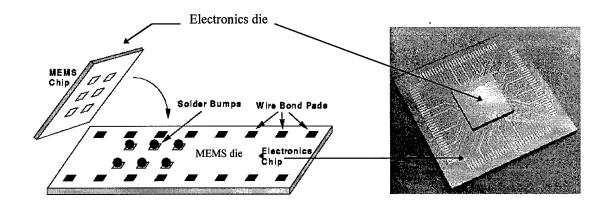

| Figure 7-4. Smartmumps flip chip attachment from MCNC                           | 7-18 |

| Figure 7-5. Examples of direct metal deposition interconnects                   |      |

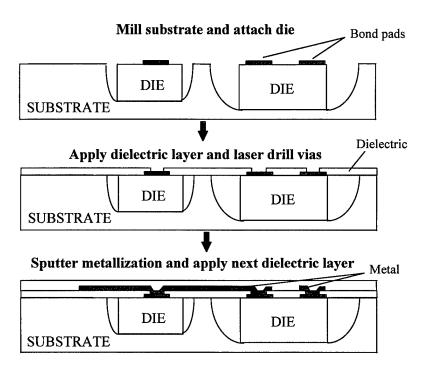

| Figure 7-6. HDI MCM fabrication flow                                            |      |

| Figure 7-7. 3-D HDI packaging by flip-chip attaching components                 | 7-22 |

| Figure 8-1. Notional view of MMS/MCM-D substrate                                |      |

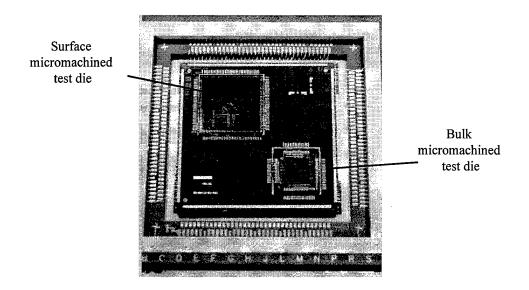

| Figure 8-2. MCM-D/MEMS package                                                  |      |

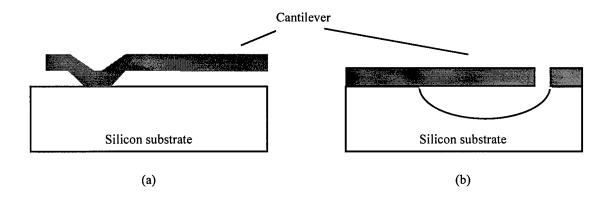

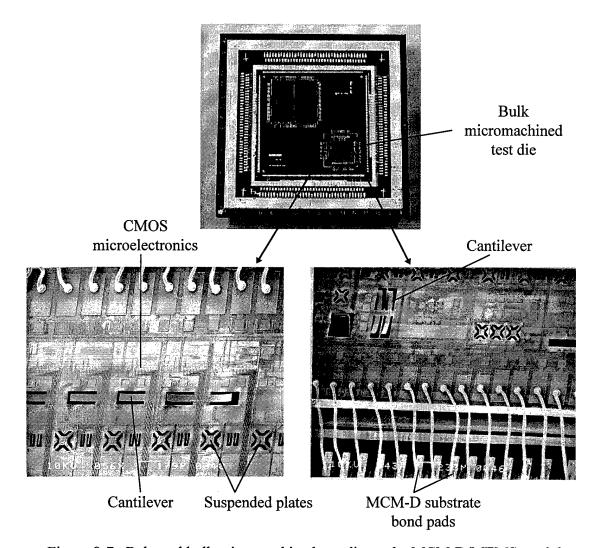

| Figure 8-3. Comparison of (a) surface and (b) bulk micromachined cantilevers    |      |

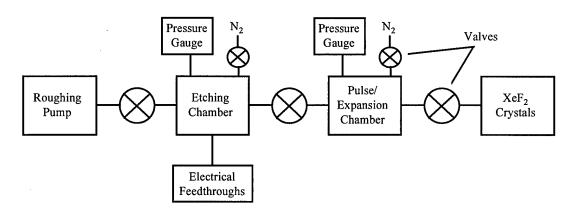

| Figure 8-4. Block diagram of UCLA XeF <sub>2</sub> etching system               |      |

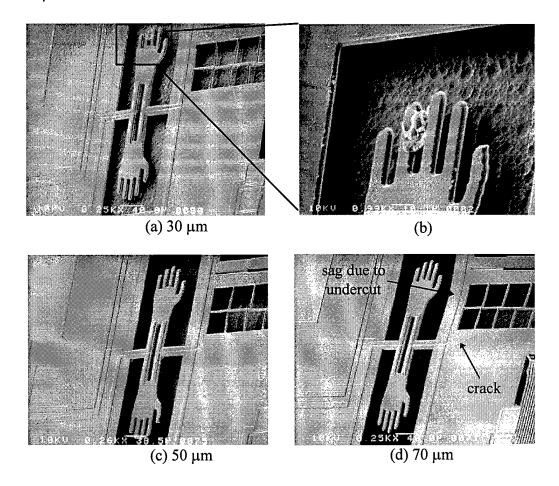

| Figure 8-5. Bulk micromachined test structure etched by XeF <sub>2</sub>        |      |

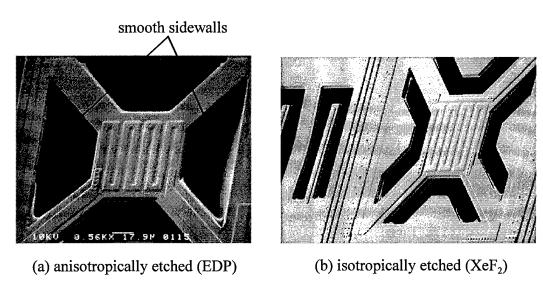

| Figure 8-6. Comparison of anisotropically and isotropically etched structures   |      |

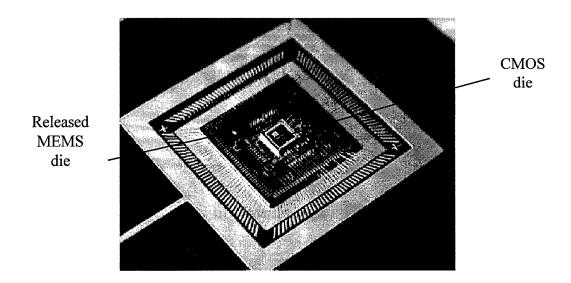

| Figure 8-7. Released bulk micromachined die on the MCM-D/MEMS module            |      |

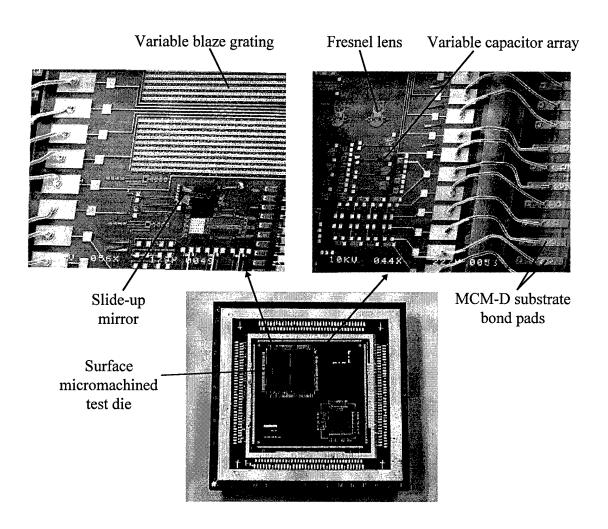

| Figure 8-8. Released surface micromachined test die on MCM-D/MEMS module        |      |

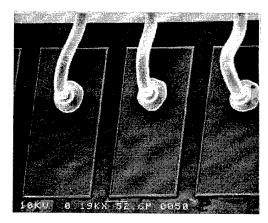

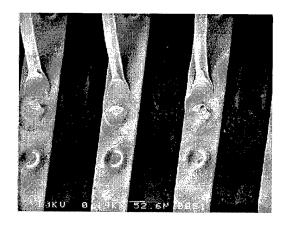

| Figure 8-9. Wirebond attachments on the (a) test die and (b) MCM-D substrate    |      |

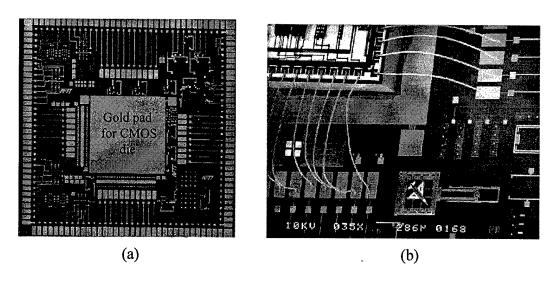

| Figure 8-10. CMOS and pre-released MEMS die packaged in a MCM-D package         |      |

| Figure 8-11. (a) MEMS die designed for attachment of CMOS controller            |      |

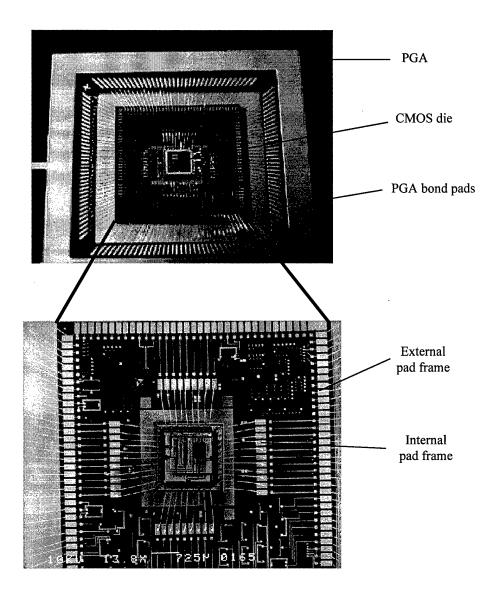

| Figure 8-12. Completed "stacked die" MCM-D in PGA-144 package                   | 8-22 |

| Figure 9-1. Standard HDI process.                                               | 9-2  |

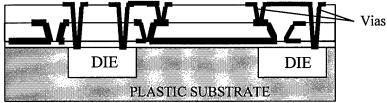

| Figure 9-2. Chip-on-Flex process flow                                           |      |

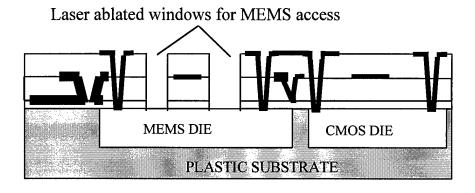

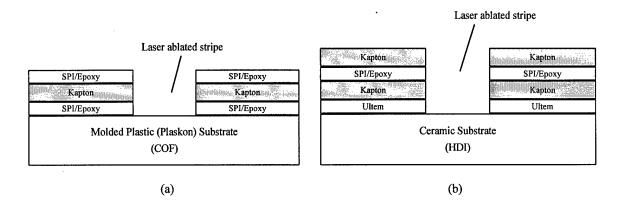

| Figure 9-3. Large area ablation for MEMS access in (a) HDI and (b) COF package. |      |

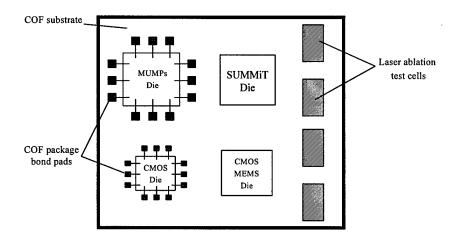

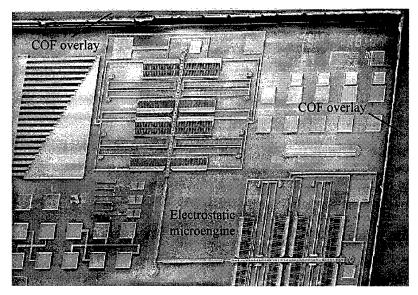

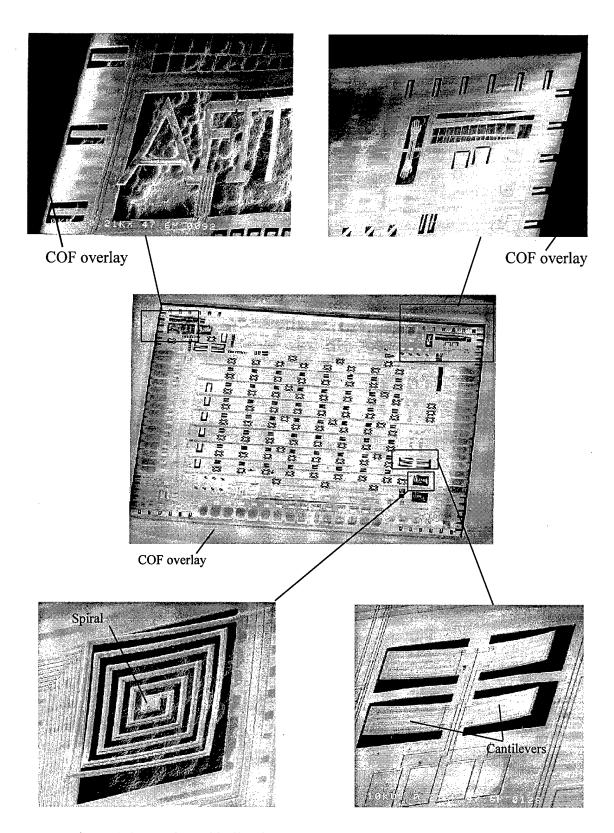

| Figure 9-4. COF/MEMS MCM fabrication layout                                     |      |

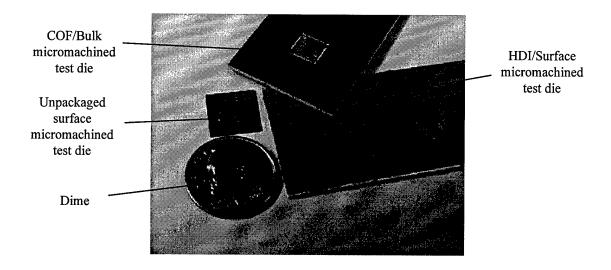

| Figure 9-5. HDI and COF/MEMS packages                                           |      |

| Figure 9-6. Close-up of HDI/MEMS MCM package.                                   | 9-10 |

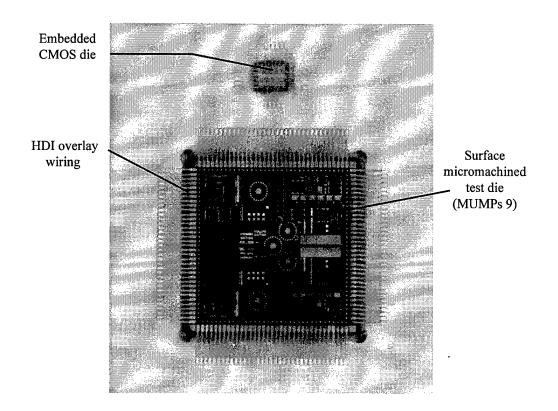

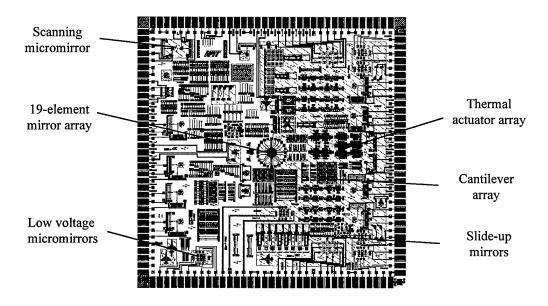

| Figure 9-7. MUMPs test die for HDI/COF Packaging.                               |      |

| Figure 9-8. Ablation pattern used for MUMPs test die                            |      |

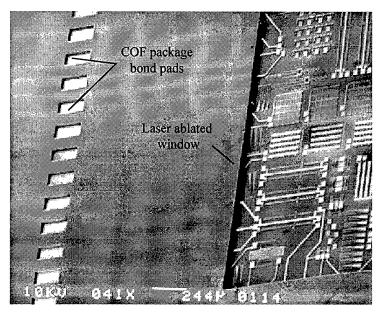

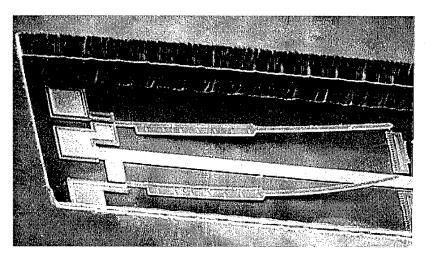

| Figure 9-9. COF package bond pads exposed through laser ablation                |      |

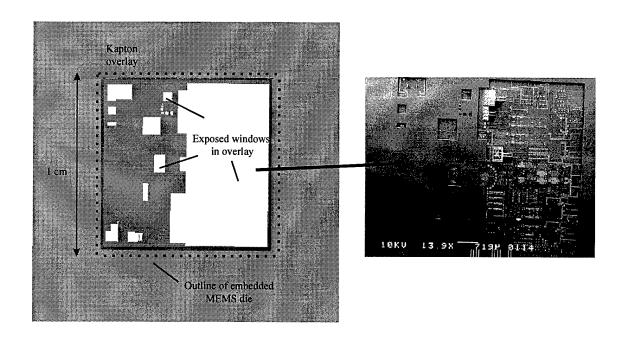

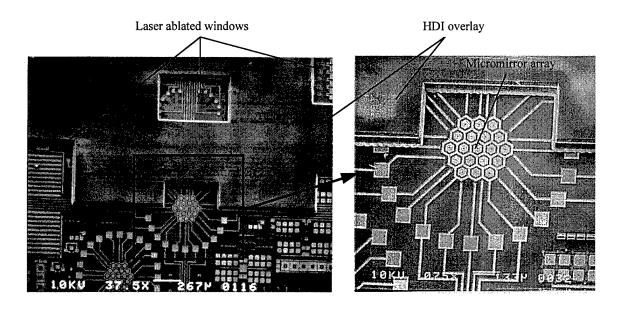

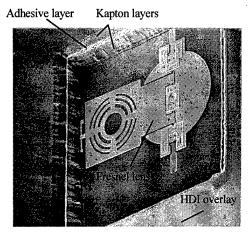

| Figure 9-10. Ablation windows in HDI overlay to expose MEMS devices             |      |

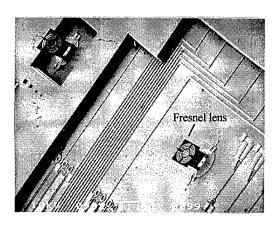

| Figure 9-11. HDI packaged surface micromachined Fresnel lens                    | 9-14 |

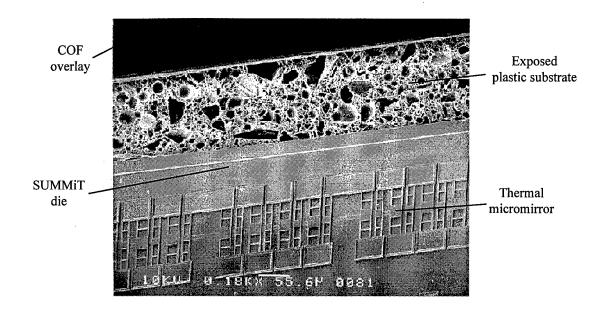

| Figure 9-12. SUMMiT surface micromachined die in COF/MEMS package 9-16                |

|---------------------------------------------------------------------------------------|

| Figure 9-13. Exposed substrate COF/MEMS package after 20 min. HF release 9-17         |

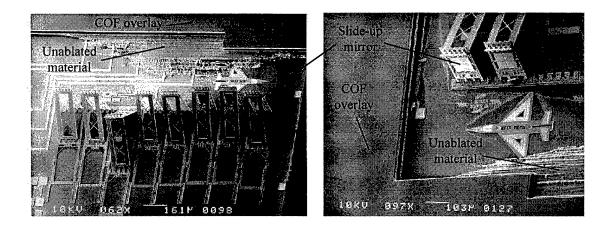

| Figure 9-14. Incomplete ablation of the Kapton overlay on COF/MEMS modules 9-18       |

| Figure 9-15. Polysilicon actuators warped due to excessive laser ablation power 9-19  |

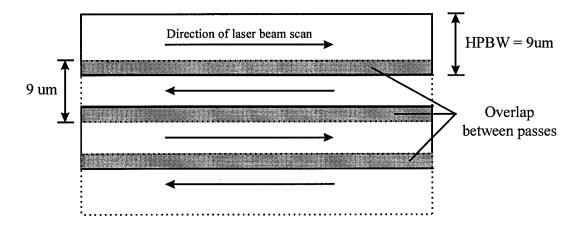

| Figure 9-16. Ablation scan pattern on HDI or COF module                               |

| Figure 9-17. Rows of unablated material due to small overlap between passes 9-22      |

| Figure 9-18. Ablation depth versus power level for COF overlay9-23                    |

| Figure 9-19. In progress view of improved ablation protocol9-27                       |

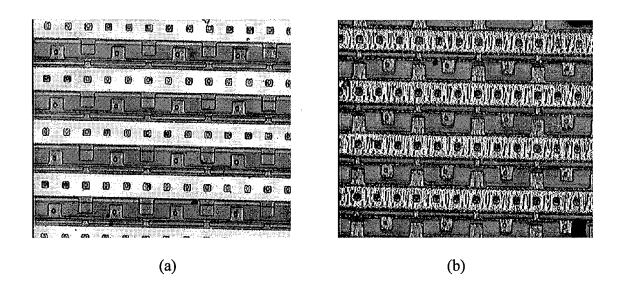

| Figure 9-20. Array of polysilicon actuators with no laser heating damage 9-28         |

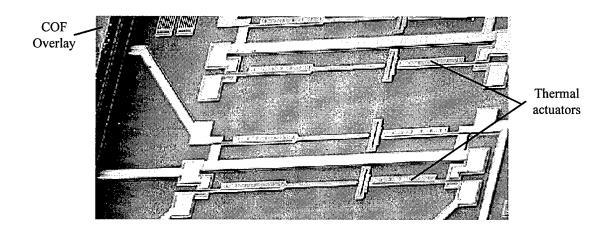

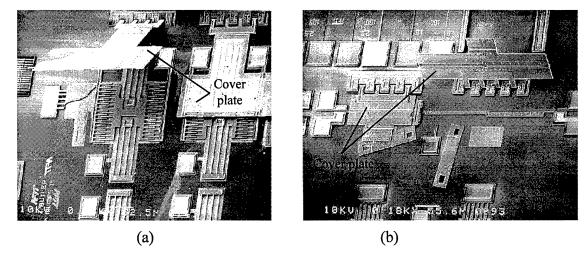

| Figure 9-21. (a) Comb resonators and (b) thermal actuators with cover plates 9-29     |

| Figure 9-22. Comparison of residue deposited on released variable blaze grating 9-31  |

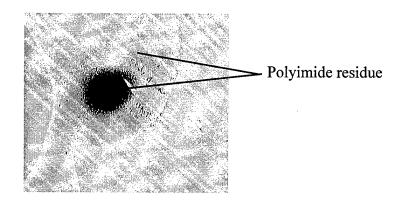

| Figure 9-23. Plasma ashed polyimide residue deposited on silicon wafer 9-35           |

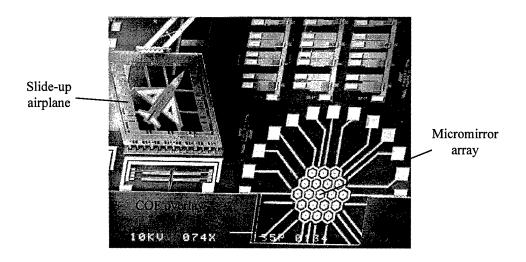

| Figure 9-24. Assembled slide-up structure on COF/MEMS package9-37                     |

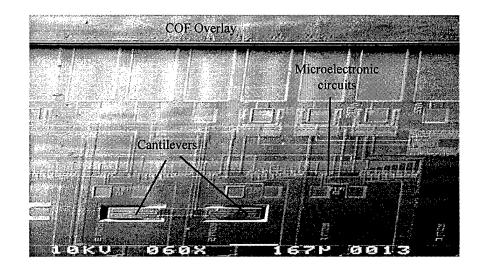

| Figure 9-25. Pre-released cantilevers on COF packaged bulk micromachined die 9-39     |

| Figure 9-26. Cross-section of (a) COF and (b) HDI package samples 9-40                |

| Figure 9-27. Released bulk micromachined test die in COF/MEMS module9-41              |

|                                                                                       |

| Figure B-1. TSUPREM 1-D phosphorus doping profileB-4                                  |

| Figure B-2. TSUPREM 2-D phosphorus doping profilesB-5                                 |

| Figure B-3. TSUPREM 3-D phosphorus doping profileB-6                                  |

|                                                                                       |

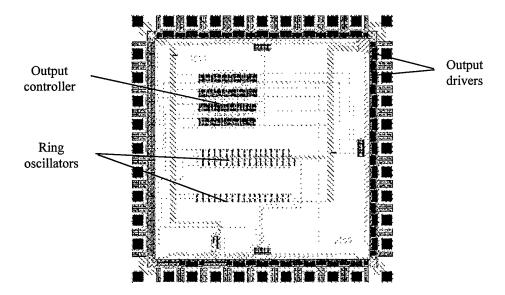

| Figure C-1. Block diagram of first CMOS ASIC                                          |

| Figure C-2. Layout of first CMOS ASIC                                                 |

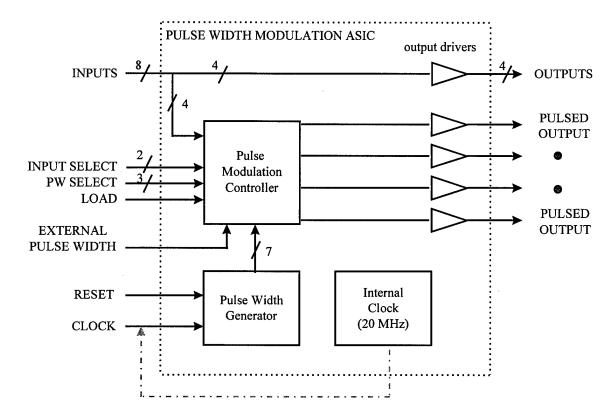

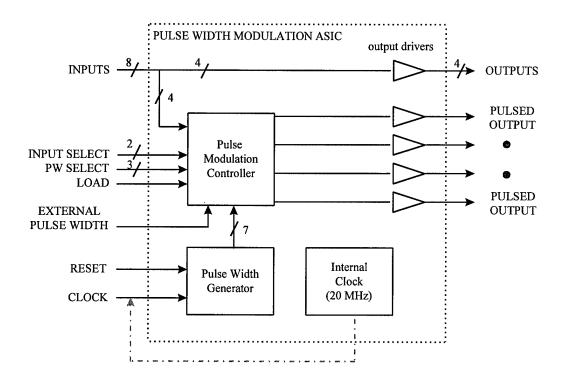

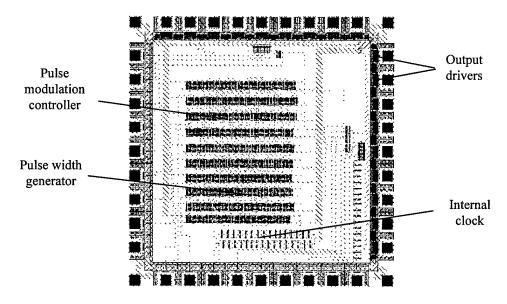

| Figure C-3. Block diagram of pulse width modulation ASIC                              |

| Figure C-4. Layout of pulse width modulation ASIC                                     |

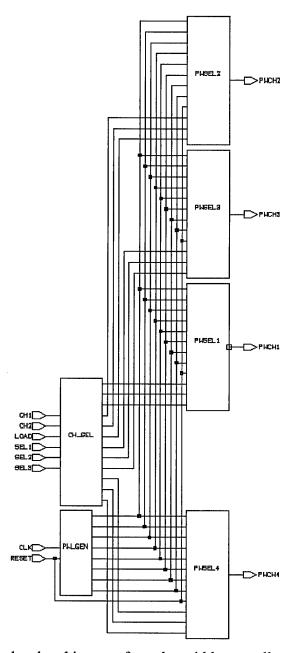

| Figure C-5. Top level architecture for pulse width controller and generator           |

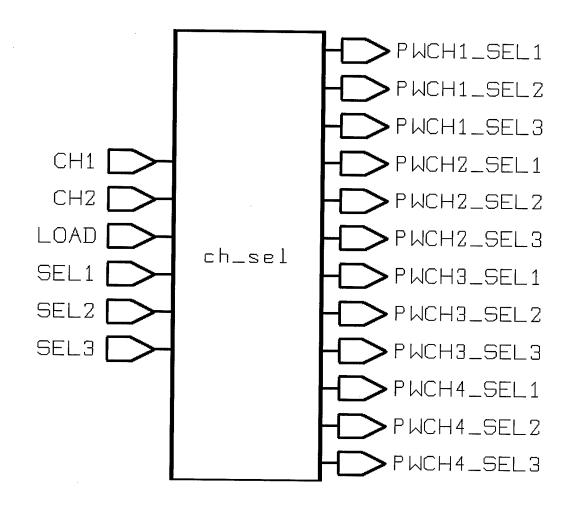

| Figure C-6. I/O ports for the channel select element of the pulse width controllerC-7 |

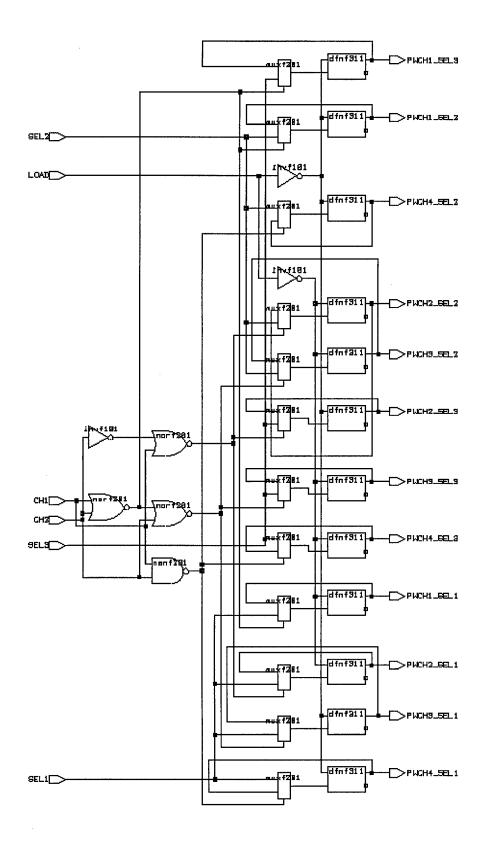

| Figure C-7. Schematic of synthesized channel select (CH_SEL) element                  |

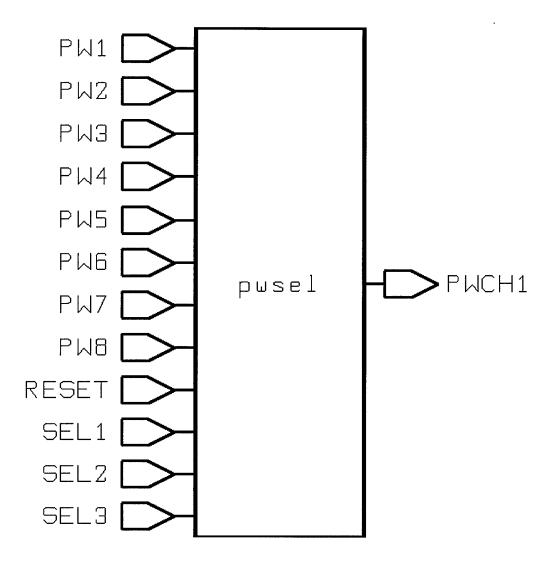

| Figure C-8. I/O ports for the pulse width select (PW_SEL) element                     |

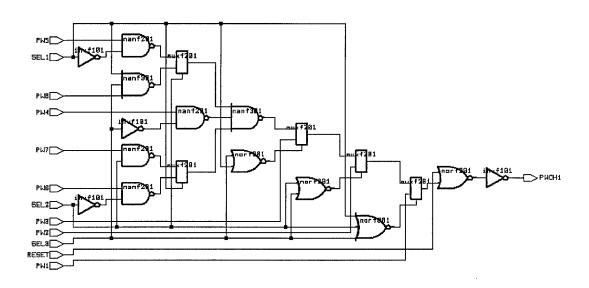

| Figure C-9. Schematic of synthesized pulse width select (PW_SEL) element              |

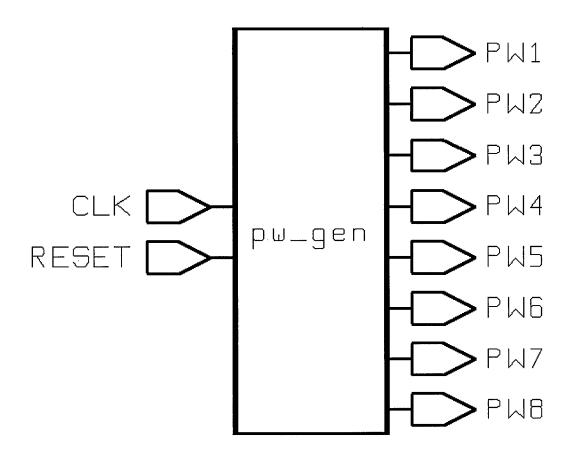

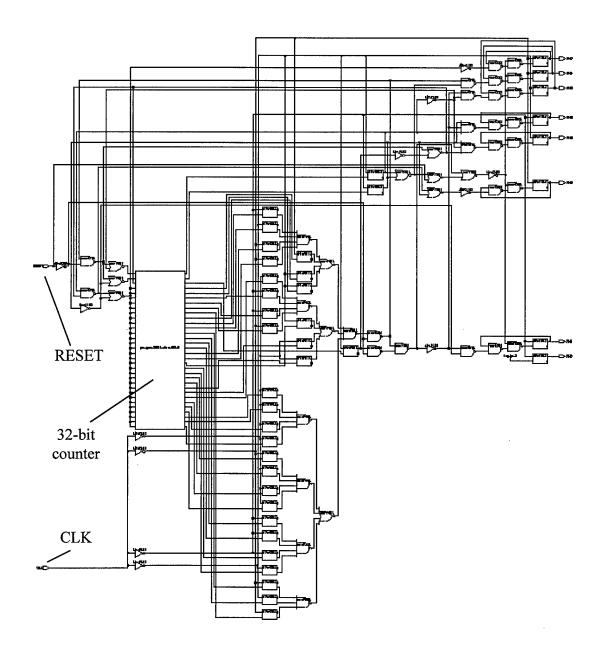

| Figure C-10. I/O ports for pulse generator (PW_GEN)                                   |

| Figure C-11. Schematic of synthesized pulse generator (PW, GEN) element               |

## List of Tables

| Table 2-1.  | Comparison of Various Etchants Used in Silicon Bulk Micromachining 2-6                    |

|-------------|-------------------------------------------------------------------------------------------|

| Table 2-2.  | Commonly Used Structural and Sacrificial Material Pairings2-10                            |

| Table 2-3.  | MUMPs Layer Names and Thickness                                                           |

|             |                                                                                           |

| Table 3-1.  | Comparison of Original and Improved Thermal Actuator Performance 3-4                      |

| Table 3-2.  | Observed Deflection for Unloaded Stressed Cantilever 3-27                                 |

|             |                                                                                           |

|             | Thermal Parameters and Their Electrical Equivalents 4-10                                  |

|             | Equations for Components shown in Figure 4-64-15                                          |

|             | Elements Used In Coupled Electro-Thermal Model 4-16                                       |

| Table 4-4.  | Material and Physical Parameters Used in Equations in Table 4-3 4-16                      |

| Table 4-5.  | SPICE Model Maximum Average Temperature of Lateral Actuator 4-24                          |

| Table 4-6.  | SPICE Model Temperature of Double Hot Arm Lateral Actuator 4-30                           |

| Table 4-7.  | Voltage and Current Required to Cause Thermal Piston Mirror Failure 4-33                  |

|             |                                                                                           |

|             | Parameter Values Used For Calculating I-V Plots in Figure 5-2 5-5                         |

|             | Measured Rs vs. Published Values5-6                                                       |

|             | MUMPs Fabrication Process As Modeled in TSUPREM5-9                                        |

|             | TSUPREM and Measured Data of Unreleased Microbridges 5-14                                 |

| Table 5-5.  | Comparison of <i>Poly 2</i> Bridge Rs vs. <i>Poly 2</i> Bridge over <i>Poly 1</i> Rs 5-16 |

| Table 5-6.  | Impact of Electrochemical Etch on <i>Poly 0</i>                                           |

|             | Electrochemical Etch Impact on Poly 1 Lateral Thermal Actuators 5-22                      |

| Table 5-8.  | Electrochemical Etch Effects on MUMPs Wiring 5-23                                         |

|             |                                                                                           |

| Table 6-1.  | SPICE Model versus Measured Average Power for Thermal Actuator 6-14                       |

| T.11. 7.1   | D. C. D. C. CMCM D. L. C.                                                                 |

|             | Performance Benefits of MCM Packaging                                                     |

|             | MIL-STD-833C Tests                                                                        |

| Table 7-3.  | Commonly Used Parameters For Evaluating Electronic Packaging 7-25                         |

| Table 8-1   | Characteristics of MCM-D Package8-2                                                       |

|             | MEMS Device Categories on Test Die                                                        |

|             | Wet Etch Release Procedure for Bulk Micromachined Test Die                                |

|             | Wet Etch Release Procedure for Surface Micromachined Test Die                             |

| 1 4010 0-4. | Wet Lien release 1 recedire for Surface Printenational Test Dis                           |

| Table 9-1.  | Characteristics of HDI and COF Packages9-4                                                |

|             | HDI/COF Release Procedure for Surface Micromachined Test Die 9-12                         |

|             | Improved Ablation Protocol for COF/MEMS Overlay9-25                                       |

|             | Recommended Cure Procedure for Accuglass T-311                                            |

|             | Film Thickness and Index of Refraction of SOG Samples                                     |

| Table 9-6. Wet Etch Release Procedure for Bulk Micromachined Test Die | 9-38 |

|-----------------------------------------------------------------------|------|

| Table 10-1. Significant Contributions and Developments                | 10-2 |

| Table D-1. Basic COF Process Sequence Flow                            | D-2  |

| Table D-2. Additional COF Processing for MEMS Packaging               | D-3  |

#### **Abstract**

Micro-electro-mechanical systems (MEMS) is a relatively new and rapidly growing field of research. Several advances to the MEMS and microsystem state of the art were achieved through the design and characterization of novel MEMS devices and packaging which are compatible with CMOS microelectronics. Empirical and theoretical models of polysilicon thermal actuators were developed to understand and simulate the behavior of thermal actuators. These models can be implemented in microelectronic circuit simulators such as SPICE and allow the simultaneous simulation of thermally actuated MEMS and microelectronics.

The most extensive investigation of the Multi-User MEMS Processes (MUMPs) polysilicon resistivity was also performed. The first published value for the thermal coefficient of resistivity (TCR) of the MUMPs *Poly 1* layer was determined as 1.25 x 10<sup>-3</sup> K<sup>-1</sup>. In addition, the sheet resistance of all the MUMPs polysilicon layers was found to be dependent on the linewidth due to the presence or absence of lateral phosphorus diffusion.

The development of robust devices and models permitted the functional and physical integration of MEMS with CMOS controllers. The functional integration of MEMS with CMOS was demonstrated through the design of automated positioning and assembly systems. A new power averaging scheme was devised to take advantage of the physical characteristics of polysilicon thermal actuators. The development of this scheme creates a whole new arena of control methodologies for MEMS.

The packaging of MEMS using foundry multichip modules (MCMs) was also demonstrated and shown to be a feasible approach to the physical integration of MEMS with other microelectronic technologies. MEMS test die were packaged using the Micro Module Systems MCM-D and the General Electric High Density Interconnect and Chipon-Flex MCM foundries. Procedures were developed and implemented for successfully releasing the MEMS die after packaging. Xenon difluoride (XeF<sub>2</sub>) was found to be an

excellent post-packaging etchant for MCM packaged bulk micromachined MEMS die. For surface micromachining, hydrofluoric acid (HF) can be used for release of MEMS after MCM packaging.

Finally, all of the MCM packages, MEMS die, and CMOS microelectronics die used in this research were foundry fabricated. In addition, a concerted effort was made to use and develop simple post-processing procedures for release and handling of the MEMS/MCM packages. The increasing availability of affordable, high performance foundry processes combined with the methodologies developed in this dissertation will allow a wide range of designers to implement robust and cost-effective microsystems.

#### Chapter 1. Introduction

The objective of this research is to investigate the development and packaging of Micro-electro-mechanical Systems (MEMS) and microelectronics. This chapter presents a summary of the problems to be solved, specific objectives, and accomplishments of this research effort as well as the organization of the document.

#### 1.1 Problem Statement and Research Objectives

The over-arching mandate for this research effort is to develop procedures or a family of procedures for effectively and reliably packaging MEMS with integrated circuits in multichip modules (MCMs) using foundry sources. Micromachining is a rapidly emerging field which is making the transition from a research novelty to commercial industry. Micro-electro-mechanical Systems (MEMS) have already found commercial applications as accelerometers, pressure sensors, ink jet nozzles, and projection displays. More complex micromachined devices are now reaching maturity with the promise of greatly reducing the size while improving system and sensor performance in a wide range of applications.

The U. S. Air Force is particularly interested in MEMS as a way of reducing the size and cost of satellites and unmanned aerial vehicles (UAVs). The life cycle cost of a satellite or air vehicle is largely dependent on the weight of the system. For example, it has been estimated that every pound of weight eliminated from the Brilliant Eyes spacecraft would result in a life cycle cost savings of 2 million dollars [1]. MEMS clearly has the potential for reducing the weight of the system. In a recent example, an

inertial navigation unit used for aircraft was replaced by a MEMS-based system weighing less than 1/20<sup>th</sup> of the original system at less than 10 percent of the cost [1]. Clearly, the Air Force and industry have strong reasons to be interested in the development and insertion of MEMS technology into many new applications.

One of the key problems addressed by this research is integration and packaging of MEMS and control circuitry in a manner that minimizes the size of microsystems while still providing superior functionality. The many advantages of micromachined systems are largely negated if they cannot be efficiently integrated and packaged with electronics [1]. Integration of MEMS and electronics is complicated by incompatibilities in the fabrication and processing of MEMS and integrated circuits. In addition, complex MEMS devices are now reaching the level of sophistication where volume production and reliability are being considered. Consequently, research dedicated to the packaging and development of microsystems is both timely and of great importance to the Air Force and the MEMS community. The Air Force Research Laboratory, the sponsor of this research, is particularly interested in integration and packaging of MEMS with other technologies using multichip modules. The use of multichip modules would provide a cost-effective means of efficiently integrating MEMS systems without the expense involved with developing unique fabrication processes.

Another critical problem addressed by this research is the ability to develop integrated MEMS systems using computer automated design (CAD) and foundry services. Several classes of MEMS such as thermally actuated devices do not have performance models suitable for use in commonly used CAD tools. Theoretical models

and accurate material characterizations are absolutely needed for the development of CAD tools for MEMS. These models are particularly important for MEMS designers planning to employ foundry processes as they provide a means of simulating the performance of systems prior to fabrication. The use of simulation enables the designer to perform numerous design iterations before expending money on foundry fabrication which typically takes two months to complete.

The problems of MEMS packaging and the development of integrated microsystems are significant issues addressed by this research. The specific objectives and questions targeted by this research are outlined in more detail in Sections 1.1.1-1.1.3.

#### 1.1.1 Are multichip module foundries suitable for MEMS?

One approach to the integration and packaging of MEMS and electronics is to use multichip modules (MCMs). MCM technology has improved dramatically over the last decade in response to requirements for better packaging and performance in microelectronics [2]. MCMs offer an attractive approach to integrating and packaging MEMS with electronics because of the ability to support a variety of die types in a common substrate without requiring changes or compromises to either the MEMS or electronics fabrication processes.

Foundry services for MEMS, MCMs, and microelectronics are available, but little research has been done to marry the various technologies to produce viable microsystems. The use of foundry services may not provide the technologically optimum solution for meeting a specific requirement as compared to a custom solution. However,

foundry services provide access to state of the art alternatives for institutions such as AFIT which can not afford the high cost of in-house fabrication facilities.

Three of the more advanced MCM foundries were investigated for MEMS packaging. The General Electric high density interconnect (HDI) and chip-on-flex (COF), and Micro Module Systems (MMS) MCM-D represent three substantially different state of the art foundry multichip module processes. HDI and COF MCMs are unique in that the die are embedded in the substrate, while the MCM-D process is a more traditional approach to packaging where the die are located on top of a patterned substrate.

Although these processes were originally developed for microelectronics, the results of this research show that they can be adapted for MEMS packaging. Key considerations for MCM packaging of MEMS include whether to release the micromachined devices before or after packaging and the compatibility of the package materials with the MEMS release procedures.

#### 1.1.2 Modeling and Simulation of MEMS Devices and Processes

Computer-aided modeling and simulation has become a key element in the success of microelectronics. Likewise, the models for MEMS devices and fabrication processes developed in support of this dissertation are important for the integration of MEMS and microelectronics. These models allow for the interaction of the MEMS devices with microelectronics and packaging to be simulated without the need for costly and time-consuming experimental trial and error. The models not only provide a means of simulating the performance of MEMS but also provide a theoretical insight into the

operation of the devices. The theoretical insights provided by the models are quite often non-intuitive and allow a greater understanding of the MEMS devices than can be achieved through empirical testing alone.

#### 1.1.3 Development of Microsystems Using MCMs

The integration of MEMS and microelectronics to produce functional microsystems was also a specific area of research. This research effort provides methods of exploiting the thermal and mechanical nature of certain MEMS devices to make them more amenable to control by CMOS electronics. In addition, key considerations for successfully designing and producing a microsystem in a multichip module are defined.

#### 1.2 Research Accomplishments

Several significant results were achieved or demonstrated during the course of this research effort. Some of the more exciting accomplishments are briefly highlighted below:

#### Multichip packaging of MEMS:

- Demonstrated feasibility of using HDI and COF for MEMS packaging.

- Proposed and demonstrated methods of reducing MEMS device damage and residue accumulation due to laser ablation during HDI/COF packaging.

- Developed procedures for using xenon difluoride (XeF<sub>2</sub>) as a tool for post packaging release of bulk micromachined MEMS.

#### Modeling and simulation of MEMS:

• Developed electrothermal SPICE model for polysilicon thermal actuators.

- Conducted experiments to produce first estimates of the thermal conductivity and thermal coefficient of resistivity of the intermediate polysilicon layer in the multiple-user MEMS processes (MUMPs).

- Generated a TSUPREM model of the MUMPs fabrication process which was used to characterize process parameters and explain resistivity variations.

#### Development of microsystems:

- Created and validated new average power control strategy for thermally actuated devices based on pulse modulation of control signals.

- Designed and demonstrated automated assembly of MEMS using CMOS controllers for flip-up structures.

#### 1.3 Organization of Dissertation

This dissertation is organized into nine chapters and a set of appendices. Chapter 1 is an overview of the research objectives and accomplishments. Chapter 2 is a primer on micro-electro-mechanical systems and discusses the main classes of MEMS fabrication. Chapter 3 contains a more focused discussion on MEMS devices developed or used during the course of this research effort. Chapter 4 describes the theory and implementation of electrothermal SPICE models for thermal actuators. Chapter 5 includes MEMS fabrication modeling work conducted to support the SPICE model and gain a better understanding of polysilicon resistance properties. The TSUPREM model of the MUMPs process is presented in this chapter and was particularly useful.

After chapter 5, the perspective broadens to functional and physical integration of MEMS with CMOS. Chapter 6 discusses the research efforts on microsystem development including the creation of the average power control scheme for thermally actuated MEMS and the CMOS chips which were designed to demonstrate this new

control methodology. Automated assembly systems using thermal actuators and the CMOS control chips are also demonstrated.

Chapter 7 discusses the fundamentals of MCM packaging as well as inherent difficulties with MEMS/MCM packaging. Chapter 8 details the MEMS/MCM-D packaging work conducted in support of this dissertation which incorporates the joint effort with Dr. Patrick Chu from the University of California at Los Angeles (UCLA) on XeF<sub>2</sub> etching of MCM packaged MEMS. Chapter 9 contains the results of HDI and COF packaging of MEMS including the various processing steps developed for mitigating MEMS device damage due to laser induced heating and residue.

The conclusions and recommendations for future research are located in Chapter 10. Finally, the appendices contain listings of items such as software code and process procedures which were deemed too long to appear in the chapter text.

#### Chapter 2. Fundamentals of MEMS Fabrication

#### 2.1 Background

Dr. Richard Feynman is credited with originating the concept of micro-electro-mechanical systems (MEMS) in a speech given in 1959 [3]. Dr. Feynman discussed the potential of several technologies which could be used for the development of microsystems and micromachines. The accuracy and prescience of Dr. Feynman's predictions on microfabrication and MEMS are remarkable.

Nonetheless, the field of MEMS was largely dormant until the late 1980's when researchers embraced the concept of leveraging the burgeoning integrated circuit fabrication industry for the construction of micromachines. As a result, current MEMS fabrication processes borrow heavily from the technology developed for the integrated circuit industry. However, the success of early micromachines, such as the single chip accelerometer shown in Figure 2-1, has led to an era of extensive research into MEMS-specific fabrication processes and materials.

There are numerous methods used to fabricate MEMS devices, and three prevalent classes of MEMS processing have matured to the stage where foundry services are available: bulk micromachining, surface micromachining, and electroplating. These processes are capable of producing unique and useful MEMS devices. Each process has unique characteristics which must be understood to make the best decision on how MEMS can be designed and employed. The following sections provide a review on these fundamental MEMS fabrication processes.

Figure 2-1. Surface micromachined, three-axis accelerometer [4]. Similar single axis devices are commonly used in airbag sensors due to their effectiveness and low cost [5].

#### 2.2 Bulk Micromachining

In bulk micromachining, the micro devices are constructed by etching a single-crystal substrate to remove portions of bulk. The structural and mechanical features of the devices are determined by thin film masks patterned on the substrate and the differing etch rates in the various crystal planes. Bulk micromachining can be used to fabricate larger devices than are achievable with surface micromachining, but the bulk process is not as flexible for creating intricate and small features. Gallium arsenide and quartz have been used as substrates; but silicon is the most common substrate material used in bulk micromachining for solid state micro sensors and actuators. Silicon is preferred because high-purity material and mature fabrication techniques are readily available at low cost as a result of the microelectronics industry. Consequently, the following descriptions will focus on silicon bulk micromachining.

Miller indices are used to define crystal planes and provide a means to describe how anisotropic etchants can be used for bulk micromachining. The Miller indices for crystal planes are shown in Figure 2-2. Amorphous and polycrystalline materials used in microelectronic processing usually etch at the same rate in all directions. This type of etching is known as isotropic etching. Conversely, the various crystal planes in a single crystal silicon substrate can be etched at different rates by using specific chemical etchants, varying doping concentrations, temperature, or other environmental factors.

Figure 2-2. Miller indices for primary crystal planes [6].

The specific phenomena which causes the etch rate to be orientation dependent is not completely understood [7]. One theory is that the density of atoms in the various crystal planes affects the rate of the etchant chemical reaction. In crystal silicon, the <111> direction has the highest density of atoms while the <100> direction has the lowest density [6]. Most anisotropic etchants etch much faster in the <100> and <110> direction [6]. For example, one of the more common anisotropic etchants is Ethylene-Diamine Pyrochatecol (EDP) which etches the <100> plane 35 times faster than in the <111>

direction [7]. A figure of merit for anisotropic etchants is selectivity which is defined as the ratio of the etch rate in the desired direction to the etch rate in other directions. Some anisotropic etchants such as potassium hydroxide (KOH) have selectivities as high as 400 with respect to the <100> and <111> directions [7].

The ability to mask or control the progress of an etchant is a key to successful micromachining. One reason anisotropic etchants such as EDP and KOH are popular choices for bulk micromachining is that they have very low etch rates for silicon oxides and nitrides [6]. Consequently, these materials can be used as masks for defining the features of devices. In addition, high doping concentrations can also be used to control the progress of the etch. For example, a high P-type doping concentration will reduce the etch rate of EDP in silicon [7]. Reductions in the etch rate of over three orders of magnitude can be achieved by using a heavy P-type boron doping greater than 2.5 x 10<sup>19</sup> cm<sup>-3</sup> [8].

Figure 2-3. Bulk micromachining example [7].

The selectivity of anisotropic etchants and the ability to effectively mask areas exposed to the etch are tools which can be used for creating devices and structures in silicon. Figure 2-3 displays a representative progression of bulk etch processing steps used for creating device structures. In this example, silicon nitride is patterned and used as an etch mask. In Figure 2-3 (c), the substrate is anisotropically etched with the etch proceeding much faster in the <100> direction as compared to the <111>. As a result, sidewalls begin to develop along the <111> direction. In Figure 2-3 (d), the etch is stopped by penetrating all the way through the silicon substrate and hitting the nitride barrier, contacting the highly doped boron etch stop, or reaching the convergence of two <111> planes. Removing the nitride completes the construction of a hole, a thin silicon diaphragm, and a V-shaped trench. Hence, the use of anisotropic etchants in combination with masking and etch controlling techniques can be used to build three dimensional structures in bulk silicon.

Isotropic silicon etchants are also used for bulk micromachining. Isotropic etchants such as the ones shown in Table 2-1 are commonly employed. Xenon difluoride (XeF<sub>2</sub>) and other gas phase silicon etchants are gaining popularity due to their high etch rates and selectivity. While isotropic etchants are useful in creating a wide array of microdevices, a potential disadvantage is the lack of an etch stop or method of controlling the etch progress. Fortunately, significant improvement has been made in controlling the etch progress by pulsing gas phase etchants and using reactive ion etching (RIE) to augment the etching process [9,10].

Table 2-1. Comparison of Various Etchants Used in Silicon Bulk Micromachining

| Etchant             | Type            | Target Crystal Plane | Etch Rate ( | A/min) |

|---------------------|-----------------|----------------------|-------------|--------|

| EDP                 | Wet anisotropic | <100>                | 10000       | [7]    |

| КОН                 | Wet anisotropic | <100>                | 7500        | [7]    |

| TMAH                | Wet anisotropic | <100>                | 6000        | [11]   |

| $HNO_3 + H_2O + HF$ | Wet isotropic   | All                  | 3000        | [12]   |

| XeF <sub>2</sub>    | Gas isotropic   | All                  | 4600        | [12]   |

| BrF <sub>3</sub>    | Gas isotropic   | All                  | 4000        | [13]   |

One of the benefits of bulk micromachined devices is that they can be constructed in silicon microelectronic processes with little modification. The CMOS MEMS process is one of the first foundry services for producing MEMS devices [14]. This process is an extension of a basic CMOS process and uses bulk micromachining to create the MEMS structures [14].