# Air Force Institute of Technology

# **AFIT Scholar**

Theses and Dissertations

Student Graduate Works

3-2002

# **Fabrication Techniques for Micro-Optical Device Arrays**

Ryan D. Conk

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Digital Communications and Networking Commons, and the Optics Commons

#### **Recommended Citation**

Conk, Ryan D., "Fabrication Techniques for Micro-Optical Device Arrays" (2002). Theses and Dissertations. 4446.

https://scholar.afit.edu/etd/4446

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact AFIT.ENWL.Repository@us.af.mil.

# FABRICATION TECHNIQUES FOR MICRO-OPTICAL DEVICE ARRAYS

**THESIS**

Ryan D. Conk, 2d Lt, USAF

AFIT/GE/ENG/02M-04

# DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

# AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

| Report Documentation Page                                                                                                     |                                                  |                                                             |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|

| Report Date<br>3 Mar 02                                                                                                       | <b>Report Type</b><br>Final                      | Dates Covered (from to)<br>Jan 01 - Mar 02                  |

| Title and Subtitle                                                                                                            |                                                  | Contract Number                                             |

| Fabrication Techniques for Arrays                                                                                             | Micro-Optical Device                             | Grant Number                                                |

|                                                                                                                               |                                                  | Program Element Number                                      |

| Author(s)                                                                                                                     |                                                  | Project Number                                              |

| 2d Lt Ryan Conk, USAF                                                                                                         |                                                  | Task Number                                                 |

|                                                                                                                               |                                                  | Work Unit Number                                            |

| Performing Organization<br>Address(es)<br>Air Force Institute of Tech<br>of Engineering and Manag<br>Street, Bldg 640 WPAFB ( | nology Graduate School<br>ement (AFIT/EN) 2950 P | Performing Organization Report Number<br>AFIT/GE/ENG/02M-04 |

| Sponsoring/Monitoring A                                                                                                       | agency Name(s) and                               | Sponsor/Monitor's Acronym(s)                                |

| Dr. Howard Schlossberg A<br>Street Arlington, VA 2220                                                                         |                                                  | Sponsor/Monitor's Report Number(s)                          |

| <b>Distribution/Availability</b> Approved for public releas                                                                   |                                                  |                                                             |

| Supplementary Notes The original document contains color images.                                                              |                                                  |                                                             |

#### **Abstract**

Micro-optical devices are vital components of conventional military data storage, sensor, and communication systems. Two types of micro-optical device arrays exist: individually addressable and matrix addressable. The matrix addressable array has a drastically reduced number of metal lines and can potentially be fabricated into large, dense (over 1k elements) arrays. Such arrays are expected to enable the development of extremely high bandwidth optical interconnect systems for future military applications including optical computing and short-haul fiber optical communication systems. I investigate new fabrication techniques for the assembly of dense matrix-addressed arrays of micro-optical devices such as vertical-cavity surface-emitting lasers. Using a micro-electro-mechanical systems (MEMS) foundry process, I design a test chip that consists of a variety of array configurations to explore possible assembly techniques. I also design a new photolithographic mask set based on assembly by flip-chip bonding and fluidic self-assembly techniques. Using my mask set, I perform basic fabrication studies and an analysis of metallization schemes for the realization of dense emitter and detector arrays. Finally, I develop and characterize three methods for array fabrication including a novel substrate trenching technique and involving the use of a spin-on polymer (poly-methyl-glutarimide or PMGI) that serves as an insulating and planarization layer between row and column metal lines.

#### **Subject Terms**

Micro-Optical Device, Matrix-Addressable Array

| Report Classification unclassified      | Classification of this page unclassified |

|-----------------------------------------|------------------------------------------|

| Classification of Abstract unclassified | Limitation of Abstract<br>UU             |

#### **Number of Pages**

111

| The views expressed in this thes                                | sis are those of the author an | d do not reflect the official |

|-----------------------------------------------------------------|--------------------------------|-------------------------------|

| policy or position of the United or the United States Governmen | States Air Force, United Sta   | ites Department of Defense,   |

|                                                                 |                                |                               |

|                                                                 |                                |                               |

|                                                                 |                                |                               |

|                                                                 |                                |                               |

## FABRICATION TECHNIQUES FOR MICRO-OPTICAL DEVICE ARRAYS

#### **THESIS**

Presented to the Faculty

Department of Electrical and Computer Engineering

Graduate School of Engineering and Management

Air Force Institute of Technology

Air University

Air Education and Training Command

In Partial Fulfillment of the Requirements for the

Degree of Master of Science in Electrical Engineering

Ryan D. Conk, B.S.E.E.

2d Lt, USAF

March 2002

Approved for public release; distribution unlimited.

# FABRICATION TECHNIQUES FOR MICRO-OPTICAL DEVICE ARRAYS

Ryan D. Conk, B.S.E.E. 2d Lt, USAF

Approved:

Lieutenant Colonel James A. Lott, Ph. D

Professor of Electrical Engineering

Thesis Advisor

Major Eric P. Magee, Ph. D

Assistant Professor of Electrical Engineering

Committee Member

Lieutenant Colonel Michael A. Marciniak, Ph. D

Assistant Professor of Engineering Physics

Committee Member

14 MAR OZ

Date

14 MAROL

Date

Date

# Acknowledgments

I would like to express my gratitude to Lt Col James A. Lott for his insight and support of this thesis. I am also indebted to the AFIT cleanroom professionals whose training and assistance was crucial. Finally, I would like to thank Lt Jennifer Manfra for the countless hours she spent in the cleanroom assuring my safety for the experiments that I performed.

Ryan Conk

# Table of Contents

| P                                                                                                                                                                                                                                                                                                                                                                                                                                                                | age                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . iv                                      |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                  | vii                                       |

| List of Tablesv                                                                                                                                                                                                                                                                                                                                                                                                                                                  | /iii                                      |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . ix                                      |

| 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                         |

| 1.1 Background 1.2 Problem Statement and Scope 1.3 Approach/Methodology 1.4 Accomplishments 1.5 Thesis Outline References                                                                                                                                                                                                                                                                                                                                        | 3<br>4<br>4                               |

| 2. Literature Review                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                         |

| 2.1 Introduction  2.2 Vertical Cavity Surface Emitting Lasers (VCSELs)  2.2.1 DBRs  2.2.2 Microcavity Active Region  2.3 Addressable Arrays  2.3.1 Individually Addressable Array  2.3.2 Matrix Addressable Array  2.4 Integration of III-V Materials with Other Substrates  2.5 Selective Oxidation  2.6 Fluidic Self-Assembly  2.7 Wafer to Wafer Transfer  2.7.1 Flip-Chip Bonding.  2.7.2 Epitaxial Lift-Off  2.8 MEMS  2.9 MUMPs®  2.10 Summary  References | 68 11 12 12 12 15 16 17 22 23 24 25 26 28 |

| 3. Design Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31                                        |

| 3.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                                        |

|                                                  | -  |

|--------------------------------------------------|----|

| 3.2 VCSEL Design                                 |    |

| 3.3 VCSEL Modeling                               |    |

| 3.4 Matrix Design Approaches                     |    |

| 3.5 Photomasks                                   |    |

| 3.6 VCSEL Photomasks                             |    |

| 3.6.1 VCSEL Photomask Design for FSA             |    |

| 3.6.2 VCSEL Photomask Design for FCB             |    |

| 3.6.3 VCSEL Photomasks for Testing               |    |

| 3.6.4 Photomask Design for Contact Bonding       |    |

| 3.7 Photomask Design for the Array               |    |

| 3.8 Photomask Design for Etch Access Holes       |    |

| 3.9 Photomask Design for Electrical Isolation    |    |

| 3.10 Photomask Design for Top Layer Metallizatio |    |

| 3.11 Self-Alignment Photomasks                   |    |

| 3.12 MUMPs <sup>®</sup> Design                   |    |

| 3.13 Resistance Comparison for Array Designs     |    |

| 3.14 Summary                                     | 55 |

| References                                       | 56 |

| 4.1 Introduction                                 |    |

| 4.2 Photolithography                             |    |

| 4.2.1 Photoresist                                |    |

| 4.2.2 Alignment and Exposure                     |    |

| 4.2.3 Development                                |    |

| 4.3 Electron Beam Metallization                  |    |

| 4.4 Etching                                      |    |

| 4.4.1 Reactive Ion Etching                       |    |

| 4.4.2 Sulfuric Acid Etch                         |    |

| 4.5 Scanning Electron Microscope                 |    |

| 4.6 Profilometer                                 |    |

| 4.7 Summary                                      |    |

| References                                       |    |

| 5. Results and Analysis                          | 68 |

| 5.1 Introduction                                 | 68 |

| 5.2 VCSEL Fabrication                            | 68 |

| 5.2.1 FSA VCSELs                                 | 68 |

| 5.2.2 FCB VCSELs                                 | 71 |

Page

|                                                                                                                                  | Page |

|----------------------------------------------------------------------------------------------------------------------------------|------|

| 5.3 MUMPs <sup>®</sup> Chip                                                                                                      | 74   |

| 5.4 Matrix Array                                                                                                                 |      |

| 5.4.1 Recess Study                                                                                                               |      |

| 5.4.2 Build-Up Study                                                                                                             | 78   |

| 5.4.3 Recess and Build-Up Study                                                                                                  | 82   |

| 5.5 Summary                                                                                                                      |      |

| References                                                                                                                       | 86   |

| <ul><li>6. Contributions, Lessons Learned, and Suggestions for Future Wo</li><li>6.1 Contributions and Lessons Learned</li></ul> |      |

| 6.2 Further Research                                                                                                             | 88   |

| Appendix A. Photolithography                                                                                                     | 90   |

| Appendix B. Metal                                                                                                                | 91   |

| Appendix C. PMGI                                                                                                                 | 92   |

| Vita                                                                                                                             | 94   |

# List of Figures

| Fig | gure                                                                                                                                                                         | Page |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

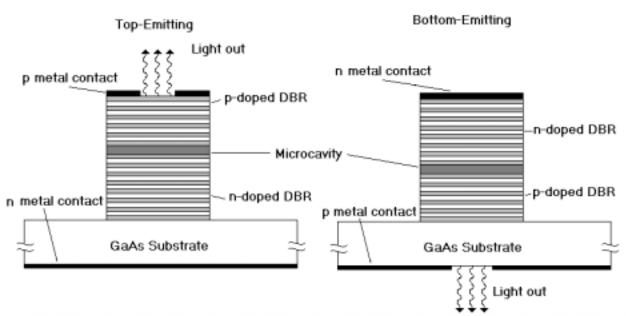

| 1.  | Top and bottom emitting VCSELs                                                                                                                                               | 7    |

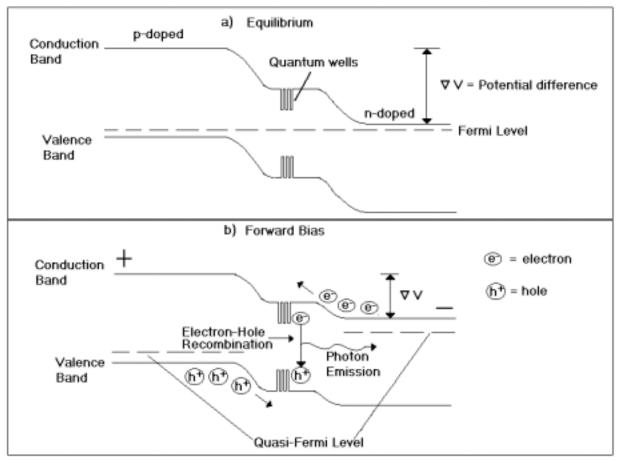

| 2.  | Energy band diagram under a) no bias and b) forward bias                                                                                                                     | 8    |

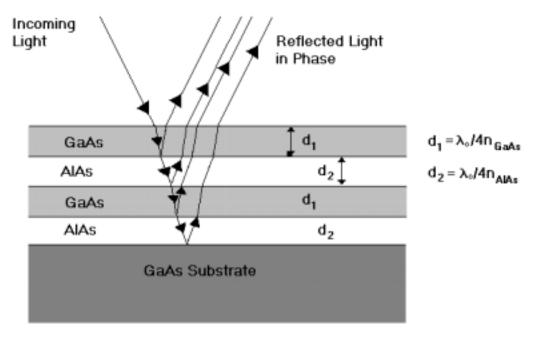

| 3.  | Illustration of constructive interference in a DBR                                                                                                                           | 10   |

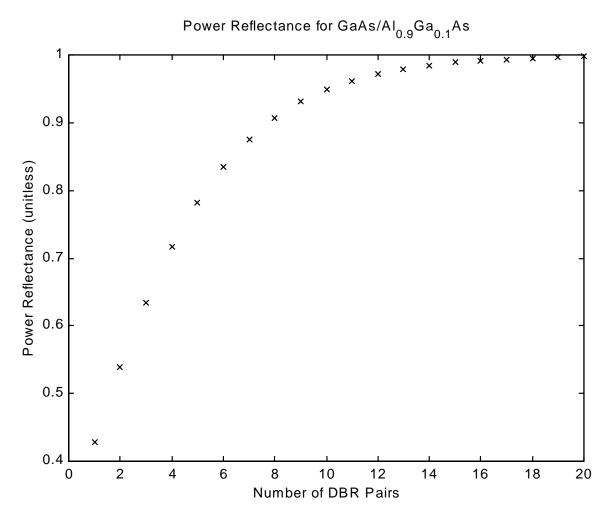

| 4.  | Power reflectance for GaAs/Al <sub>0.9</sub> Ga <sub>0.1</sub> As DBR pairs with air as incident Medium and GaAs as the substrate                                            | 11   |

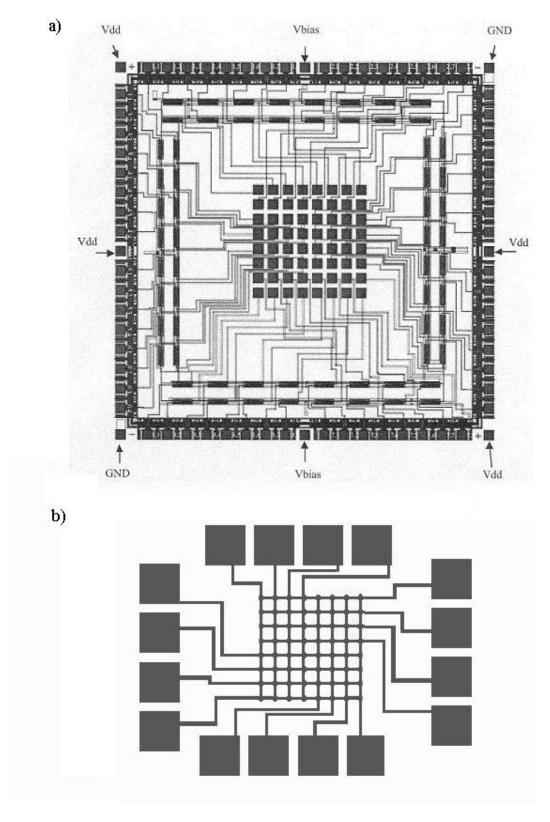

| 5.  | Comparison of an a) individually addressable array [10] and a b) matrix addressable array. Forty-eight additional lines and bond pads are required for the individual array. | 13   |

| 6.  | Matrix Addressing                                                                                                                                                            | 14   |

| 7.  | Schematic cross-section of a matrix addressable VCSEL array design                                                                                                           | 15   |

| 8.  | Oxidation rate dependence on a) AlAs mole fraction, b) layer thickness, c) temperature, and d) time                                                                          | 18   |

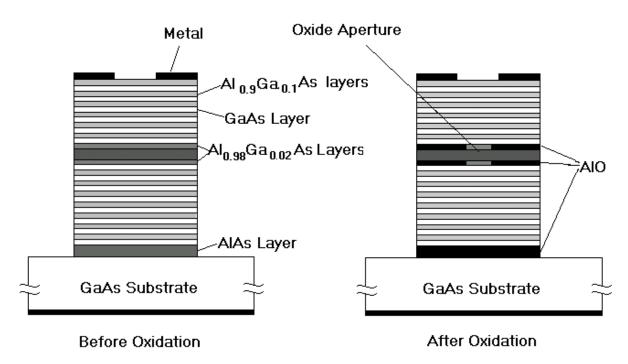

| 9.  | Before and after oxidation for a lift-off VCSEL                                                                                                                              | 19   |

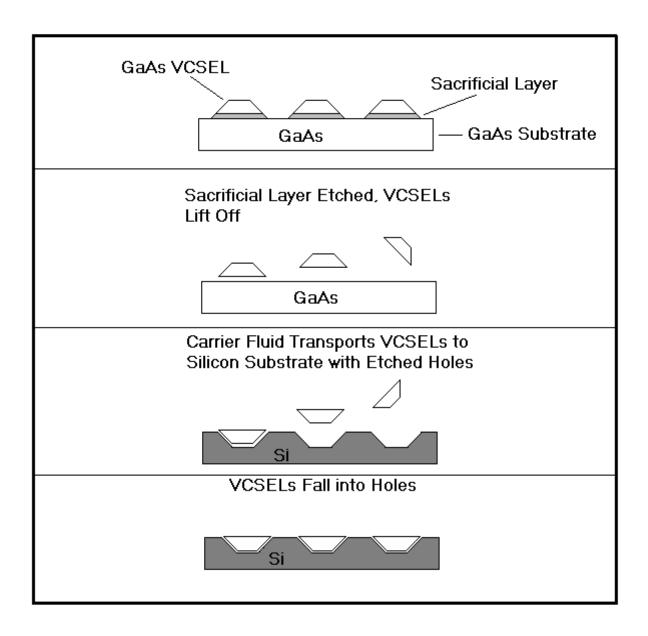

| 10. | FSA process for integration of GaAs VCSELs with a Si substrate                                                                                                               | 20   |

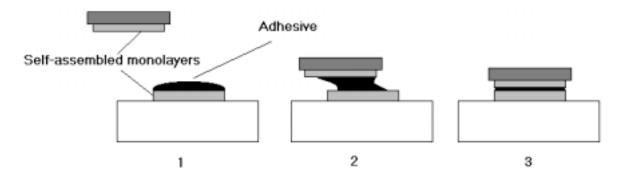

| 11. | Self-alignment utilizing capillary forces                                                                                                                                    | 22   |

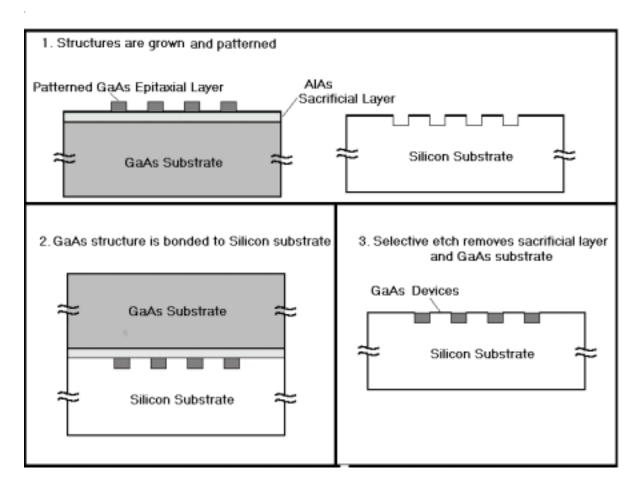

| 12. | Flip-chip bonding of GaAs epitaxial grown VCSELs onto a Si substrate                                                                                                         | 24   |

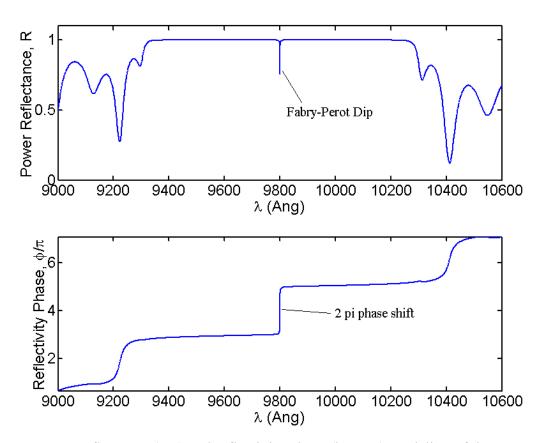

| 13. | Power reflectance (top) and reflectivity phase (bottom) modeling of VCSEL structure bias                                                                                     | 33   |

| 14. | Modeling of electric field intensity and index of refraction in the VCSEL                                                                                                    | 34   |

| 15. | Standing electric field intensity modeling in the quantum wells                                                                                                              | 34   |

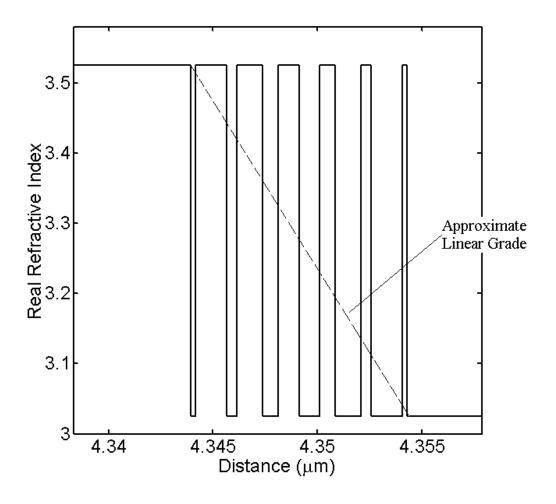

| 16. | Al <sub>0.9</sub> Ga <sub>0.1</sub> As and GaAs graded index layer                                                                                                           | 35   |

| Fig | ure                                                                                                                                                                              | Page |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

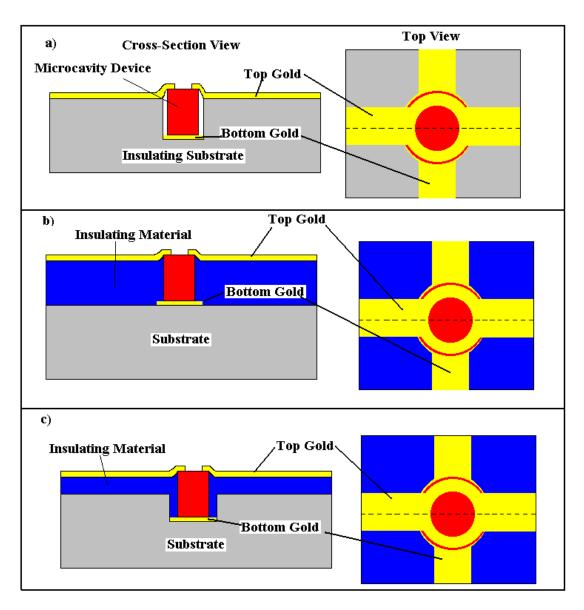

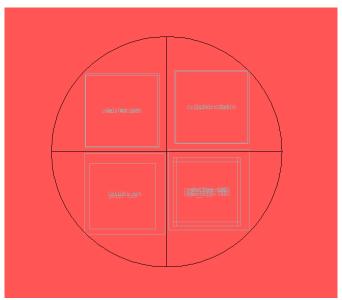

| 17. | Illustration of three different design approaches a) etched insulating substrate, b) spun on insulating material, and c) combination of etched substrate and insulating material | 36   |

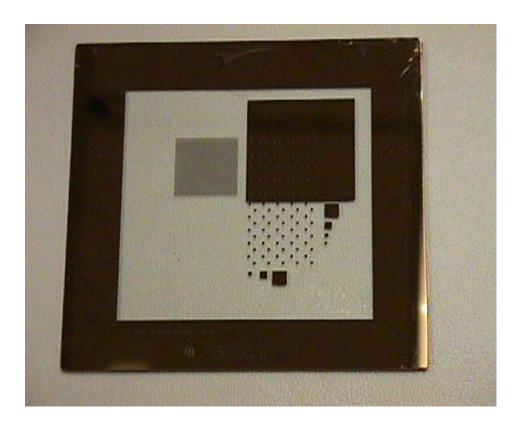

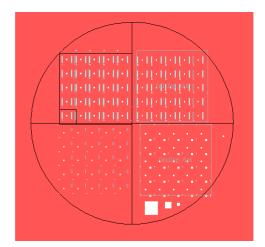

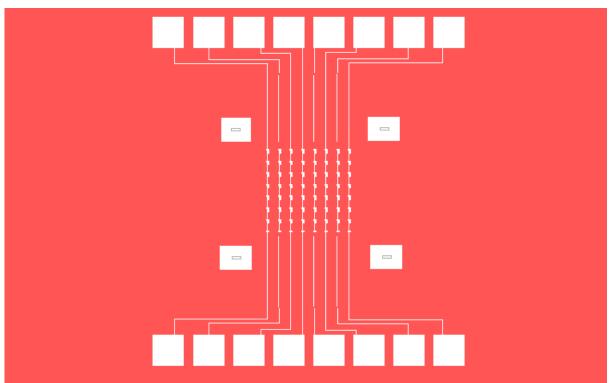

| 18. | Picture of photomask #1                                                                                                                                                          | 37   |

| 19. | L-Edit layout of photomask 1                                                                                                                                                     | 38   |

| 20. | L-Edit layout of photomask 2.                                                                                                                                                    | 38   |

| 21. | L-Edit layout of photomask 3                                                                                                                                                     | 39   |

| 22. | Design of VCSELs for FSA                                                                                                                                                         | 40   |

| 23. | VCSEL design of 8 x 8 array for FCB                                                                                                                                              | 40   |

| 24. | Ring contact design for on-wafer testing                                                                                                                                         | 41   |

| 25. | On wafer testing design for 8 x 8 FCB VCSEL array                                                                                                                                | 42   |

| 26. | Photomask design for metallization of VCSELs                                                                                                                                     | 43   |

| 27. | Etch design for one 8 x 8 array                                                                                                                                                  | 44   |

| 28. | Close-up of disk in the etch design                                                                                                                                              | 44   |

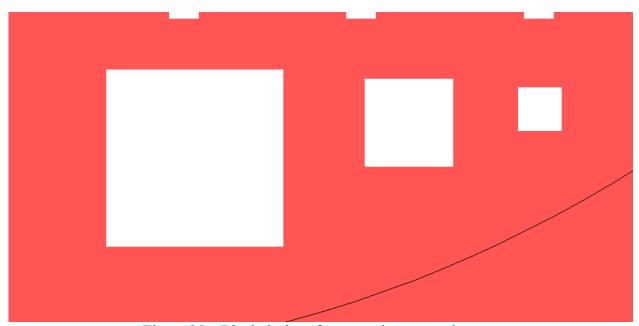

| 29. | Demonstration of how metal fits in the recess                                                                                                                                    | 45   |

| 30. | Etch access hole design                                                                                                                                                          | 46   |

| 31. | Layout of ring design used for electrical isolation photomask                                                                                                                    | 47   |

| 32. | Design for top layer metallization                                                                                                                                               | 47   |

| 33. | Close-up of top metal contacts                                                                                                                                                   | 48   |

| 34. | Block designs for self-alignment                                                                                                                                                 | 49   |

| 35. | Block designs for recess in target substrate                                                                                                                                     | 49   |

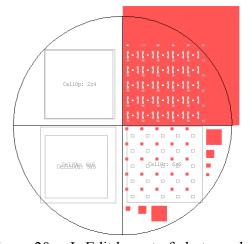

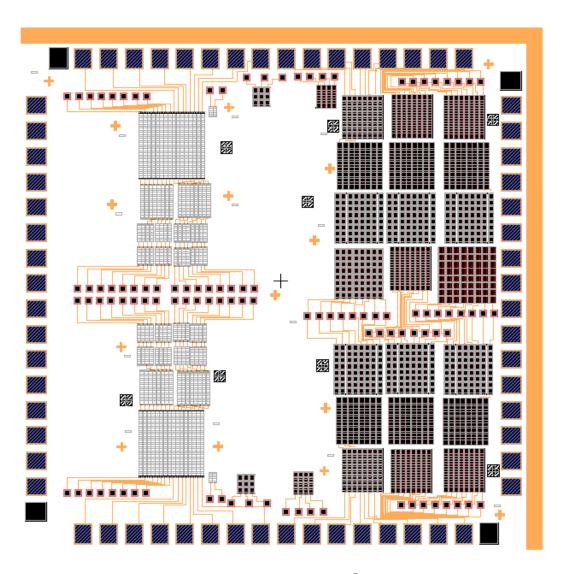

| 36. | L-edit layout of MUMPs® design                                                                                                                                                   | 50   |

| Fig | ure                                                                                                                                                                                                | Page |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

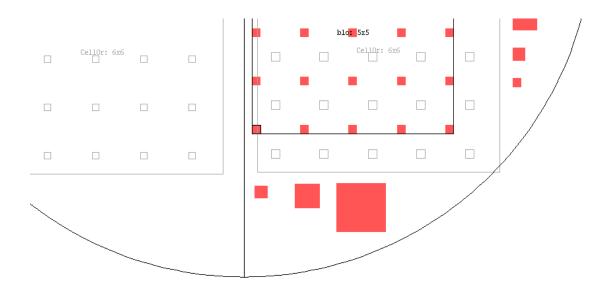

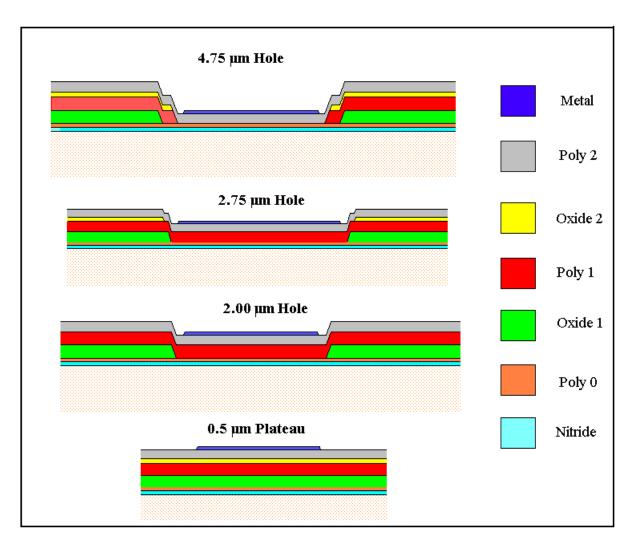

| 37. | L-edit design of various hole depths that were included on the MUMPs® chip                                                                                                                         | 51   |

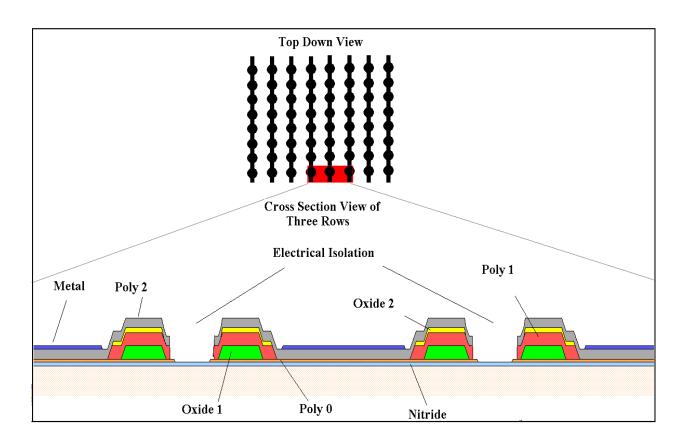

| 38. | L-edit cross-sectional view of MUMPs® design illustrating electrical isolation                                                                                                                     | 52   |

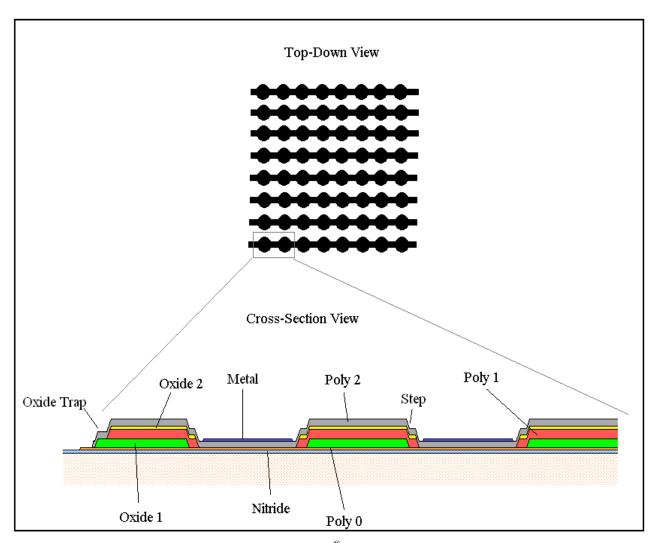

| 39. | L-edit cross-section view of MUMPs® design demonstrating oxide trapping and step drop-offs                                                                                                         | 53   |

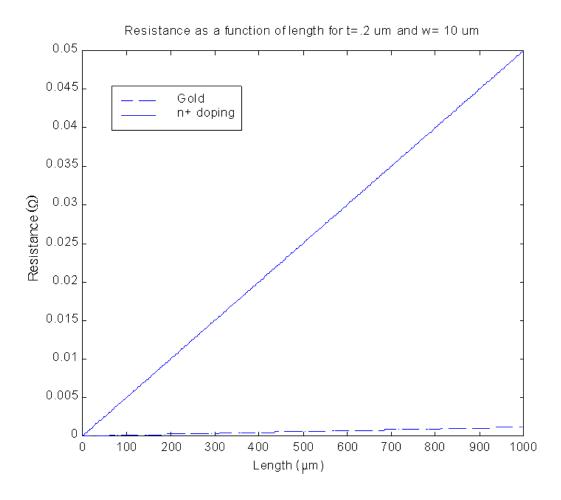

| 40. | Plot of the total resistance of a gold line and a $10^{18}$ cm <sup>-3</sup> Si doped GaAs line of width 10 $\mu$ m and a thickness of 0.2 $\mu$ m as the length is varied form 0 to 1000 $\mu$ m. | 55   |

| 41. | Karl Suss MJB3 Mask Aligner located in the AFIT cleanroom                                                                                                                                          | 59   |

| 42. | Electron beam evaporator located in the AFIT cleanroom                                                                                                                                             | 61   |

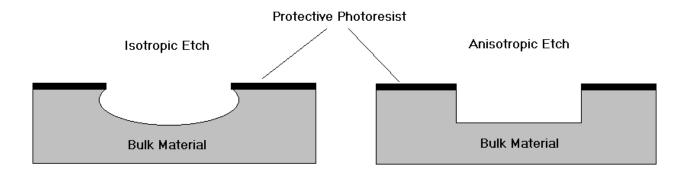

| 43. | Illustration of an isotropic and an anisotropic etch                                                                                                                                               | 62   |

| 44. | Phantom RIE system                                                                                                                                                                                 | 63   |

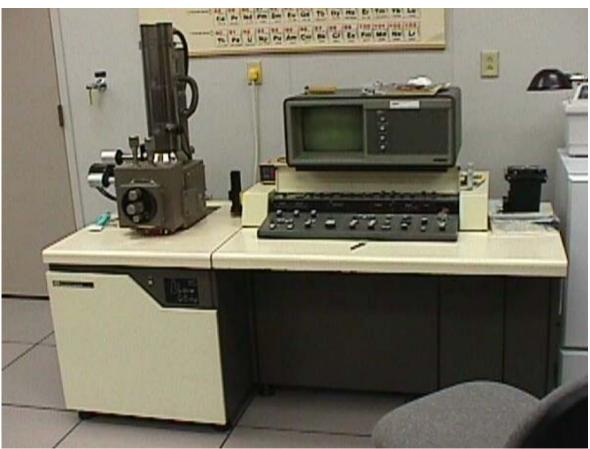

| 45. | Scanning Electron Microscope located in the AFIT test room                                                                                                                                         | 64   |

| 46. | Tencor Alpha Step 200 Profilometer located in the AFIT cleanroom                                                                                                                                   | 65   |

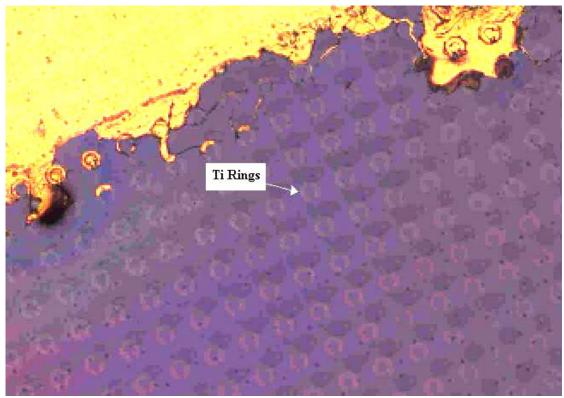

| 47. | Microscope image of VCSEL wafer with Ti rings remaining on wafer after metal lift-off. Gold rings should be on top of the Ti rings                                                                 | 69   |

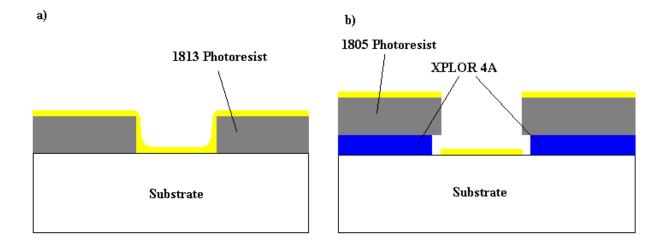

| 48. | Illustration of a) Possible problem of continuous gold coating and b) How undercutting of XPLOR 4A can alleviate this problem                                                                      | 70   |

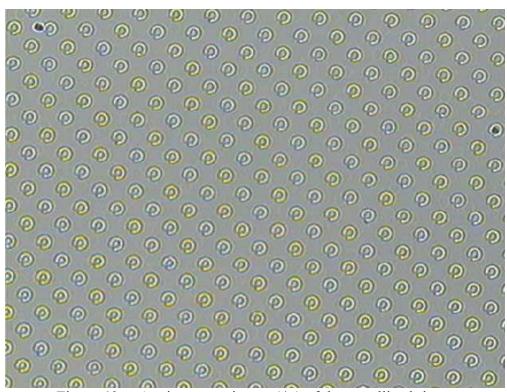

| 49. | A microscope image (4x) of the metallized rings                                                                                                                                                    | 70   |

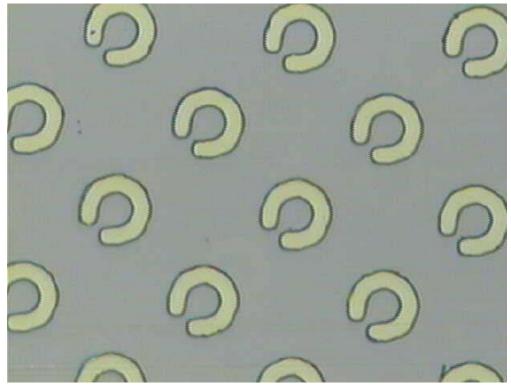

| 50. | Microscope image (20x) of metallized rings                                                                                                                                                         | 71   |

| 51. | Microscope image (50x) showing gold circles                                                                                                                                                        | 72   |

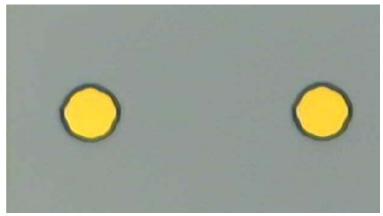

| 52. | Microscope image (50x) of the metallized array                                                                                                                                                     | 72   |

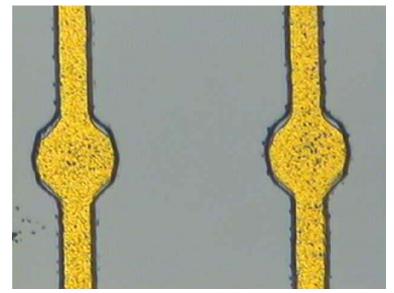

| 53. | Microscope image (30x) of array after wet etch was performed. These two gold rings were the only ones remaining on the entire wafer                                                                | 73   |

| Fig | ure                                                                                                                                                                                                        | Page |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 54. | SEM photo (1100x) of mesas after wet etch was performed. Picture clearly shows that the sulfuric acid etched far into the sides of the device                                                              | 73   |

| 55. | SEM photo (350x) of mesas after wet etch                                                                                                                                                                   | 74   |

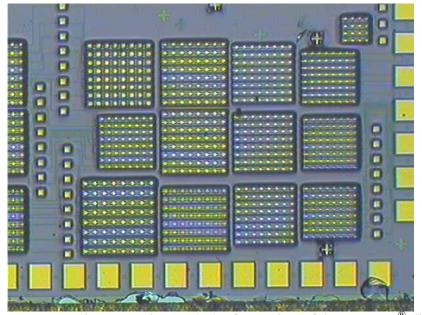

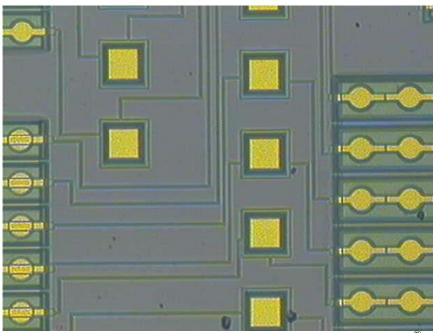

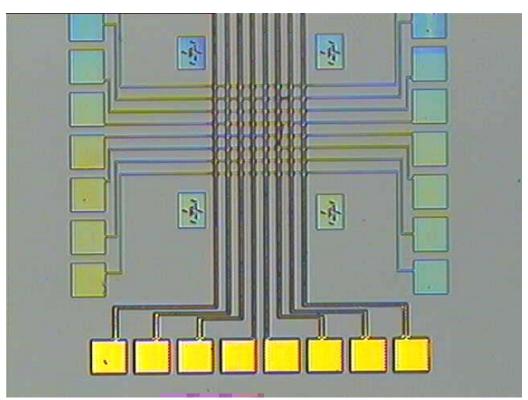

| 56. | Microscope image (4x) of a portion of the MUMPs die                                                                                                                                                        | 75   |

| 57. | Microscope image (10x) of one array                                                                                                                                                                        | 75   |

| 58. | Microscope image (10x) of two varying array designs                                                                                                                                                        | 76   |

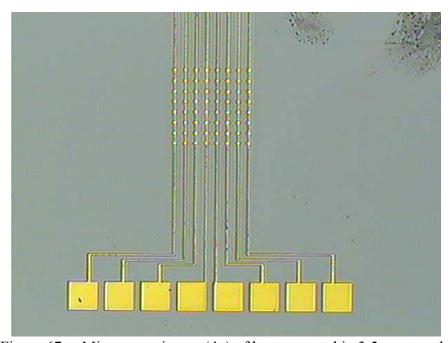

| 59. | Microscope image (10x) showing metal routing between arrays and bond pads                                                                                                                                  | 76   |

| 60. | Microscope image (50x) showing the isolation between adjacent rows                                                                                                                                         | 77   |

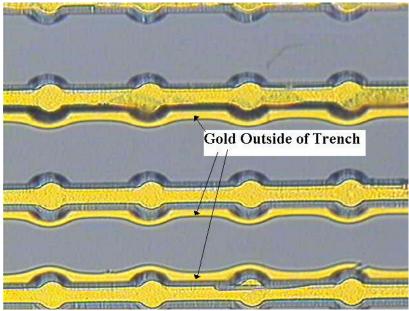

| 61. | Microscope Image (20x) of bottom gold lines inside an 8 µm trench. The trench caused the photoresist to spread unevenly over the wafer resulting in the gold depositing onto the sides of the trenches.    |      |

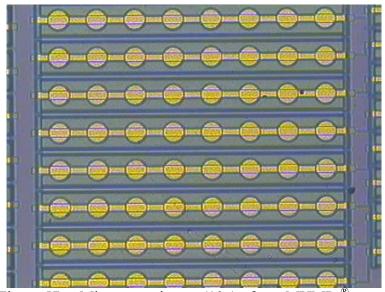

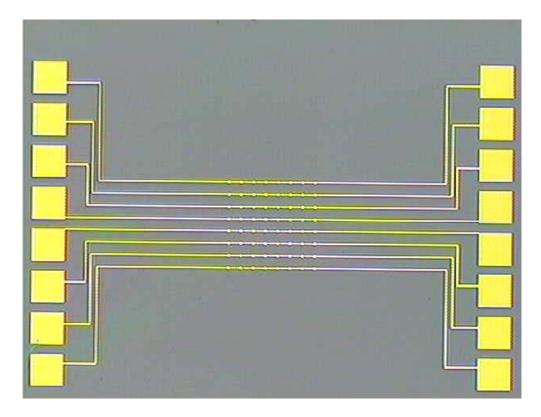

| 62. | Microscope image (4x) of bottom metallization array                                                                                                                                                        | 80   |

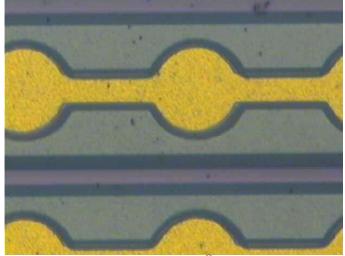

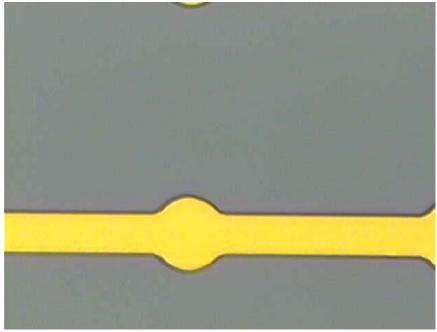

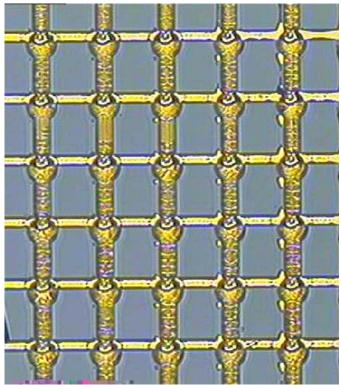

| 63. | Microscope image (50x) of bottom metallization. Image focuses on one line and one circle. The circle is where the VCSEL would be placed                                                                    | 80   |

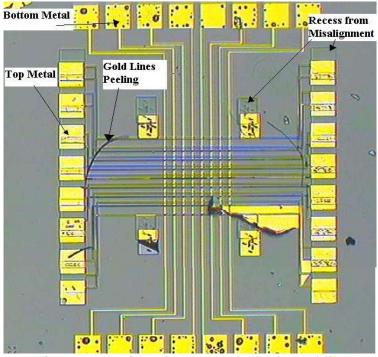

| 64. | Microscope image (4x) of matrix array. The horizontal lines are running on top of the deposited PMGI layer. Some of the lines did not bond well to the PMGI and are peeling off                            | 81   |

| 65. | Microscope image (30x) illustrating the matrix array. The shadow shows the misalignment and subsequent recess of the PMGI. The top layer metallization is 1.4µm higher that the bottom layer metallization | 81   |

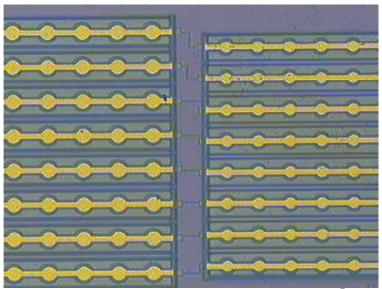

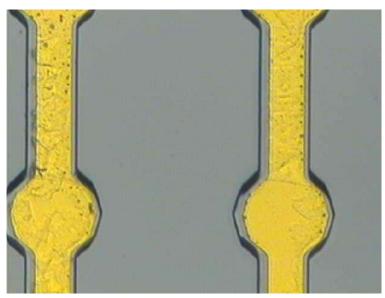

| 66. | Microscope image (50x) of metallization in 3.5 μm trench                                                                                                                                                   | 83   |

| 67. | Microscope image (4x) of bottom metal in 3.5 μm trench                                                                                                                                                     | 83   |

| 68. | Microscope image (50x) of metal in 2 μm trench                                                                                                                                                             | 84   |

| 69. | Microscope image (4x) of the patterned photoresist on top of the PMGI SF11                                                                                                                                 | 84   |

| Figure |                                                                | Page |

|--------|----------------------------------------------------------------|------|

| 70.    | Microscope image (20x) of the bottom metallization and the top |      |

|        | metallization running over them                                | 85   |

# <u>List of Tables</u>

| Table                                     | Page |

|-------------------------------------------|------|

| 1. MUMPs® Layers and Thickness            | 27   |

| 2. MUMPs <sup>®</sup> Lithography Options | 27   |

#### **Abstract**

Micro-optical devices are vital components of conventional military data storage, sensor, and communication systems. Two types of micro-optical device arrays exist: individually addressable and matrix addressable. The matrix addressable array has a drastically reduced number of metal lines and can potentially be fabricated into large, dense (over 1k elements) arrays. Such arrays are expected to enable the development of extremely high bandwidth optical interconnect systems for future military applications including optical computing and short-haul fiber optical communication systems.

I investigate new fabrication techniques for the assembly of dense matrix-addressed arrays of micro-optical devices such as vertical-cavity surface-emitting lasers. Using a micro-electro-mechanical systems (MEMS) foundry process, I design a test chip that consists of a variety of array configurations to explore possible assembly techniques. I also design a new photolithographic mask set based on assembly by flip-chip bonding and fluidic self-assembly techniques. Using my mask set, I perform basic fabrication studies and an analysis of metallization schemes for the realization of dense emitter and detector arrays. Finally, I develop and characterize three methods for array fabrication including a novel substrate trenching technique and involving the use of a spin-on polymer (poly-methyl-glutarimide or PMGI) that serves as an insulating and planarization layer between row and column metal lines.

#### FABRICATION TECHNIQUES FOR MICRO-OPTICAL DEVICE ARRAYS

#### 1. Introduction

#### 1.1 Background

Since their development in the early 1960's, semiconductor lasers have made significant contributions in many optical areas involving communications, data storage, and sensors. Edge-emitting lasers, the first to be commercialized and most common semiconductor laser in use today, can be found in bar code scanners, laser pointers, advanced optical memories (CD-ROMs), digital video disk (DVD) players, printers, and multi-channel optical fiber communications [1]. With the recent development of oxide apertures that significantly lower the threshold current and increase the power efficiency, vertical-cavity surface-emitting lasers (VCSELs) have become a more attractive choice for systems that require semiconductor lasers since they offer many advantages over edge-emitting lasers. VCSELs are less expensive, smaller, and easier to fabricate then edge-emitting lasers. In addition, dense two-dimensional VCSEL arrays, as well as arrays of resonant cavity light emitting diodes (RCLEDs) and resonant cavity photodetectors (RCPDs), can be fabricated on a single wafer. One-dimensional edge-emitting laser arrays are readily fabricated, but two-dimensional edge-emitting laser arrays require extensive processing and assembly.

In fabricating micro-optical device arrays, the limiting factor on the size of the array is not the actual devices themselves, but the metal connections required to activate the devices. Micro-optical devices operate by placing a current across the device. To induce the current flow, two

metal connections must be placed on the device, a bottom and top contact. In individually addressable arrays, each device must have at least one of its own metal lines. However, for matrix addressable arrays, devices share lines. Therefore, matrix addressable arrays allow for much denser and larger arrays. The drawback with matrix addressable arrays is that some control is lost over which devices can be turned on at a given time.

The ability to integrate micro-optical device arrays with integrated circuits is critical for the development of optoelectronic integrated circuits (OEICs). The main application for OEICs is telecommunications. With wavelength division-multiplexing and dense wavelength division multiplexing, integration has the potential to offer significant performance improvements [2]. A potential application for integrated VCSEL arrays is in relaying information between or within computers. As very large-scale integrated (VLSI) circuits and ultra large scale integrated (ULSI) circuits reach the limitations of silicon technology, alternative foundries must be utilized to continue advancing the performance of today's electronics. Multi-GHz bandwidth optical interconnects from board to board or chip to chip offer an attractive solution to the electrical interconnect problems of signal integrity and cross-talk at high frequencies [4].

Two primary techniques have been developed to fabricate two-dimensional micro-optical device arrays. The first method is to deposit metal on the backside of a doped substrate to provide a common ohmic contact for all of the devices, grow the devices on the wafer, and then provide an individual contact for each device. The other method is to create heavily doped channels on the substrate with devices on them. The channels are electrically isolated from one another. Finally, metal rows are placed across the tops of the devices, perpendicular to the doped channels to enable matrix addressing of devices.

The ability to fabricate large dense arrays using these techniques is hindered either by the number of metal connections required or the resistance of the doped line. Alternative design approaches and innovative fabrication techniques are required to overcome these limitations. One possible solution is to take advantage of the matrix addressing design and use gold lines to reduce the resistance. This solution, however, contains a new set of fabrication and design problems. There are two main concerns that need to be addressed, each with their own problems. The first being that the metal lines need to contact both the top and bottom surface of the device while electrical isolation must be maintained to avoid cross-talk between active lines and inactive lines. Secondly, the devices cannot be grown directly on top of the metal, therefore, the devices must be transferred onto the lines.

#### 1.2 Problem Statement and Scope

The purpose of this thesis is to study and develop fabrication steps that enable matrix addressing of micro-optical devices using metal lines for electrical contacts. Various approaches will be attempted and analyzed to fabricate the matrix array. Fabrication studies will be conducted on the processing of actual microcavity light-emitter devices. Both flip-chip bonding (FCB) and fluidic self-assembly (FSA) processes will be discussed as possible techniques for the integration of the micro-optical devices onto the array.

I performed all of the photolithography, wet etching, and metal lift-off steps in the AFIT cleanroom. Technicians at the Air Force Research Laboratory's Sensors Directorate cleanroom performed the UV exposure. Metal was deposited onto the wafer at both facilities. The microcavity light-emitter composition was grown at the University of New Mexico [3].

#### 1.3 Approach/Methodology

The first thing that I did was to design the prototype photolithography masks that would be needed to fabricate the VCSELs and the matrix-addressable arrays. In addition, a Multi-User MEMS Process (MUMPs®) chip was designed to explore various foundry configurations for the foundation of the array. I then performed studies on the processing of light-emitter devices so that they can be integrated into the array. Finally, I conducted studies to develop fabrication techniques for the matrix addressable array.

# 1.4 Accomplishments

For this thesis, I performed a numerical analysis of the microcavity light-emitting devices used for this study. I calculated and compared the resistance for a gold line compared to an n<sup>+</sup>-doped GaAs line. I designed prototype photomasks necessary for the processing of the matrix addressable array and the devices. I also designed a MUMPs® chip and had it fabricated. I laid down ring contacts for the development of the microcavity light-emitter devices and performed a wet etch study for the mesa formation of the devices. I was also able to develop three potential methods for the fabrication of a low resistance matrix addressed micro-optical device array.

## 1.5 Thesis Outline

In Chapter 2, I discuss previously published research relevant to this thesis. In Chapter 3, I describe my design approach and mask layouts and present my numerical analysis and resistance calculations. Chapter 4 then outlines essential experimental equipment and procedures. Chapter 5 contains the experimental results and analysis. Finally, Chapter 6 contains my conclusions and recommendations for future work.

# References

- 1. EMCORE homepage. Excerpt from unpublished article. n. pag. http://www.emcore.com/html\_documents/Application\_notes/d1\_visible\_lasers.htm. November 29, 2001.

- 2. Lerner, E. J., "Optoelectronic Integrated Circuits Promise Simplicity", *Laser Focus World*, vol. 33, no.6, June 1997.

- 3. Stintz, A, University of New Mexico.

- 4. Tuantranont, A., V. M. Bright, J. Zhang, W. Zhang, J. Neff, Y. C. Lee. "MEMS Controllable Microlens Array for Beam Steering and Precision Alignment in Optical Interconnect Systems", *Technical Digest 2000 Sensor and Actuator Workshop*, pp. 101-104, June 4-8, 2000.

#### 2. Literature Review

#### 2.1 Introduction

In this chapter, I first discuss the operation and structure of the VCSEL. I then present the two types of arrays, the individually addressable and the matrix addressable, that have been previously fabricated and compare the benefits and limitations of each. Fluidic self-assembly, epitaxial lift-off, and flip-chip bonding are discussed as successful integration methods for the transfer of micro-devices from one substrate to another. Selective oxidation and its importance for device lift-off is then presented. A brief overview of MEMS and the MUMPs® process concludes the chapter.

#### 2.2 Vertical Cavity Surface Emitting Lasers (VCSELs)

While this thesis involves micro-optical device array structures, I will focus on the VCSEL. The VCSEL is one of the most ubiquitous micro-optical devices. Its structure and operation are simply more complex versions of the other micro-optical devices. Other micro-optical devices include the resonant cavity light emitting diode (RCLED), which is a VCSEL structure with fewer distributed Bragg reflector (DBR) periods, and the resonant cavity photo detector (RCPD), which is an RCLED that absorbs light rather than emits it.

VCSELs are semiconductor lasers that emit a beam of light perpendicular to their planar surface. VCSELs consist of doped DBR mirror stacks and a microcavity active region. The DBRs function as mirrors for the device and the microcavity is designed to be a resonant cavity by requiring its thickness to be an integer multiple of  $\lambda/2$ , where  $\lambda$  is the DBR design wavelength. There are two basic types of VCSELs, bottom-emitting and top-emitting [6]. In bottom-emitting VCSELs, the bottom DBR has a lower reflectance than the top DBR and light is

emitted through the substrate. For bottom-emitting VCSELs, the substrate must be transparent at the operating wavelength. In top-emitting VCSELs, the top DBR has fewer layers than the bottom DBR, thereby giving the top DBR a lower reflectance. The metal contact typically has a circular aperture to allow the light out. Figure 1 illustrates example bottom and top-emitting VCSEL structures.

Figure 1 Top and bottom emitting VCSELs.

Light is created in the VCSEL by forward biasing the p-i-n junction that is formed from the doped DBRs and the unintentionally doped microcavity. When a forward bias voltage is applied, the potential difference between the n-doped DBR and the p-doped DBR is reduced. This causes electrons and holes to flow across the device in opposite directions. Once in the microcavity, the electrons and holes are confined in narrow regions called quantum wells, where the energy band gap is small relative to the rest of the structure. Once trapped, the electrons and holes recombine with each other and light energy is released in the form of a photon. Figure 2 illustrates this

process. As the photons reflect off the DBRs and reenter the microcavity, they cause other electron-hole pairs to recombine. This results in the stimulated emission of photons. If more photons are created than are lost in one round trip through the cavity, the VCSEL will begin to lase.

Figure 2 Energy band diagram under a) no bias and b) forward bias.

## 2.2.1 DBRs

Unlike an edge-emitting laser which has a large gain region with a length of a couple of hundred micrometers, a VCSEL has a total gain region on the order of a few hundred Angstroms. The gain region is the area of the device where photons are created. Consequently, the VCSEL's

mirrors must have a very high reflectivity in order for the optical gain to be greater than the loss [24]. Though metal mirrors are highly reflective, they have absorptive losses. Metal mirrors can only achieve a reflectivity of approximately 98% with the rest of the energy lost in the material by absorption. VCSELs require a DBR reflectance of 99% to 99.99%. To avoid absorption, semiconductor materials are used to make the VCSEL's DBRs. This results in the required high mirror reflectance. The semiconductor material reflects a portion and transmits the remaining energy. The reflectance at the interface of two different nonabsorbing materials at normal incidence is

$$R = \left(\frac{n_1 - n_2}{n_1 + n_2}\right)^2$$

(unitless)

where R is the power reflectance, and  $n_1$  and  $n_2$  are the real indexes of refraction of the two materials [11]. A quick calculation using Equation 1 shows that a substantial difference in the indexes of refraction is needed to obtain a high reflectance. For example, the GaAs-air interface has R = 0.31 (31%) at 980 nm. Semiconductor materials do not offer a large index difference  $(\Delta n = |n_1 - n_2|)$ . The solution to this problem is to use a DBR with many periods.

The idea behind the distributed Bragg reflector is that the total reflectance can be increased if a series of reflecting surfaces is used. Constructive interference occurs when the initial reflected wave is in phase with subsequent reflecting waves forming a strongly reflected wavefront. Figure 3 illustrates a DBR with strong constructive interference. A DBR consists of alternating high index and low index layers. For constructive interference, the thickness of each layer needs to be  $\lambda_o/4$ n-thick, where  $\lambda_o$  is the design wavelength and n is the index of refraction of the layer. A DBR pair consists of a high and low index layer. The reflectance for a series of DBR

Figure 3 Illustration of constructive interference in a DBR.

pairs (valid only for integer number of pairs at normal incidence) for nonabsorbing layers is

$$R = \left[ \frac{1 - \frac{n_s}{n_0} \left( \frac{n_1}{n_2} \right)^{2m}}{1 + \frac{n_s}{n_0} \left( \frac{n_1}{n_2} \right)^{2m}} \right]^2$$

(unitless)

where n<sub>s</sub> is the index of refraction for the substrate, n<sub>o</sub> is the index for the incident medium, n<sub>1</sub> and n<sub>2</sub> are the indexes for the high and low layers, and m is the number of DBR pairs [12]. As the number of DBR pairs increase, the total reflectance will also increase as shown in Figure 4. Aluminum arsenide (AlAs) and GaAs are the most common materials used for the DBRs because of their relatively large difference in index of refraction, but more importantly because of their similar lattice constants. The similar lattice constants allow many AlAs/GaAs DBR pairs to be grown with very few defects.

Figure 4 Power reflectance for GaAs/Al<sub>0.9</sub>Ga<sub>0.1</sub>As DBR pairs with air as the incident medium and GaAs as the substrate.

## 2.2.2 Microcavity Active Region

A VCSEL operates by generating light in a narrow gain region of the device, usually in quantum wells. The microcavity is the resonant cavity of the VCSEL and contains the quantum wells. The microcavity is extremely small, typically only a few  $\lambda$  thick. To obtain resonance in the microcavity, the thickness of the microcavity must be an integer multiple of  $\lambda_o/(2n_{\mu c})$ , where  $\lambda_o$  is the design wavelength and  $n_{\mu c}$  is the index of refraction of the microcavity.

#### 2.3 Addressable Arrays

Two types of two-dimensional VCSEL arrays have been fabricated. The individually addressable array and the matrix addressable array have both been successfully demonstrated. Several groups have fabricated matrix addressable VCSEL arrays by directly growing the devices onto a GaAs substrate [13][14][20]. Prather fabricated an 8 x 8 individually addressable VCSEL array integrated with a CMOS driver array using flip chip bonding [16]. Tuantranont et al. fabricated a MEMS/VCSEL hybrid system by flip-chip bonding an individually addressable VCSEL array with a microlens mirror array [21]. These are just a few examples of the VCSEL arrays that have been fabricated.

- 2.3.1 Individually Addressable Array. In the individually addressable array, each VCSEL has at least one of its own metal contacts. The most common method of design is to make one plane a ground contact for all of the devices. Contacting each VCSEL with a metal lead creates the positive voltage to the device, thereby allowing each device to be operated independently. As a result, any single device, all of the devices, or any combination of devices can be turned on at the same time. The drawback for the individually addressable array is that for an N-by-N array, N<sup>2</sup> metal lines are required. Array sizes are thereby seriously limited by the number of metal lines and bond pads that can be placed onto the wafer. Figure 5 shows the comparison of an individual and a matrix addressable 8x8 array.

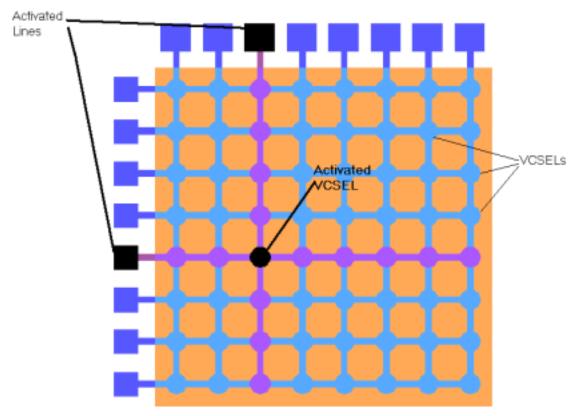

- 2.3.2 Matrix Addressable Array. For the N x N matrix-addressable array, N metal lines run horizontally across the structure to make up either the ground or positive contact, while the other contact is made of N metal lines that run vertically across the device. For the matrix addressable array, only 2N metal lines are required. At each intersection of the lines, a VCSEL is placed, so that the device has both contacts connected to it. When the lines are active, all devices that are

Figure 5 Comparison of an a) individually addressable array [10] and a b) matrix addressable array. Forty-eight additional lines and bond pads are required for the individual array.

at an intersection of two active lines will be turned on as demonstrated in Figure 6. The problem regarding the matrix addressable array is the inability to have complete control over the VCSELs when more than one is required to be activated. The matrix addressable array only allows control for a single VCSEL, any number of VCSELs in a single column or row, or all of the VCSELs.

Figure 6 Matrix addressing.

In VCSEL array structures, the limiting factor in the number of VCSELs is the number of metal connections or wires that is required to operate the VCSELs. Matrix addressable arrays greatly reduce the number of metal lines that are required for the array. In comparison, for an 8 x 8 array, 64 metal lines are required for the individually addressed array but only 16 metal lines are required for the matrix-addressable array. For the same number of lines that are required for

the 8 x 8 individually addressable array, a 32 x 32 matrix addressable array can be fabricated. This results in an additional 960 VCSELs that can be placed in the array.

The technique that has been used to fabricate the matrix addressable array is to heavily dope a GaAs layer. The doped layer functions as the bottom metal contact. The device material is then grown and patterned on top of the doped layer. Next, ions are implanted between rows of devices in the doped GaAs layer. The ions neutralize regions of the n<sup>+</sup> doping and create an insulating layer between rows of the doped GaAs layer [13]. Finally, metal column lines are routed across the device to create the other metal contact. Figure 7 shows a schematic of this design. The heavily doped GaAs rows sit on a semi-insulating GaAs substrate and have a much higher resistivity than gold. The resistivity of these GaAs rows is a limiting factor for the size of the array.

Figure 7 Schematic cross-section of a matrix addressable VCSEL array design [13].

## 2.4 Integration of III-V Materials with Other Substrates

The ability to integrate micro-devices from one wafer to another is thought to be a critical requirement to fabricate a matrix addressable array using gold lines. The devices can not be

grown directly on top of the gold, so they must be transferred. This type of hybrid integration has many benefits such as the ability to combine microelectronic circuitry with optical devices and has been successfully demonstrated with a variety of fabrication techniques.

Integrating III-V compound semiconductor devices with silicon substrates is a difficult task. The simplest approach has been to grow the structure in a monolithic process. However, heteroepitaxial growth of GaAs on Si produces unreliable devices [24]. The process suffers from lattice mismatch between the materials, which results in many dislocations and often poor device performance. The other approach is to grow the two materials separately and then place the III-V devices onto the Si substrate. Because of the extremely small size of the devices and materials, one cannot simply pick up the devices and place them onto the substrate. With ordinary objects, gravity is the dominating force. However, on the micrometer scale other forces, mainly adhesive forces, become significant. Adhesive forces are due to surface tension, van der Waals forces, and electrostatic forces [2]. These forces can cause the devices to stick to gripper tools rather than simply dropping when released. In addition, this method is too time consuming in order to fabricate a dense array of devices. Three approaches have been developed that avoid these problems. Fluidic self-assembly, flip chip bonding, and epitaxial lift-off offer the ability to integrate III-V optical devices with silicon.

#### 2.5 Selective Oxidation

One of the fundamental fabrication steps in all of the integration methods is the removal of the devices from the substrate. The ability to separate the GaAs epitaxial layer from the GaAs bulk substrate is achieved through the selective oxidation of epitaxial AlAs and AlGaAs layers. Researchers at the University of Illinois developed an aluminum oxide (AlO) that was mechanically stable and had a low index of refraction, unlike other gallium and arsenide

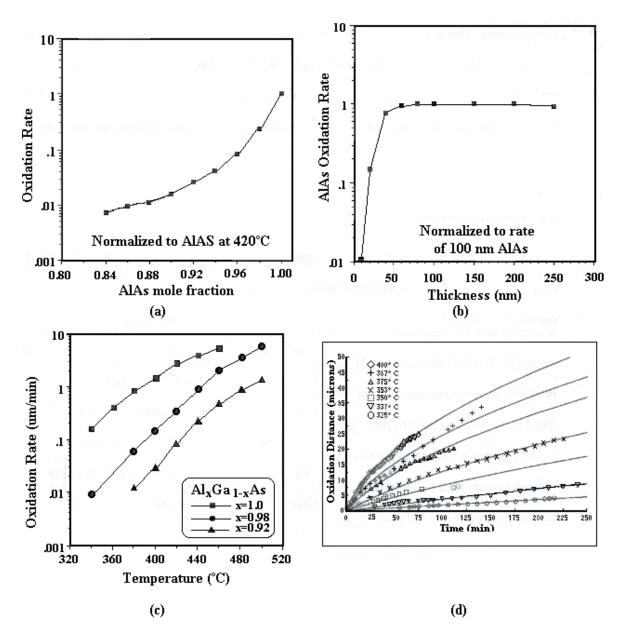

oxides [1]. The conversion of the epitaxial AlAs or AlGaAs layers to the oxide (AlO or AlGaO) is achieved by introducing a water vapor to exposed surfaces of AlAs or AlGaAs at high temperatures [1]. The oxide can then be selectively etched using hydroflouric acid or potassium hydroxide, freeing the epitaxial layer from the substrate. Figure 8 shows the oxidation rates for varying AlAs mole fractions, thicknesses, temperatures, and times.

Additionally, the oxidation of AlGaAs has significantly enhanced the performance of VCSEL devices through the use of oxide apertures. The oxide is a dielectric and forms an abrupt oxidation front. By oxidizing the AlGaAs layer so that only the AlGaAs in the middle of the device remains, carriers are forced into this region when the device is turned on. Figure 9 illustrates oxidation of the AlAs and GaAs layers. Active regions of a few microns can thereby be defined providing optical confinement and the ability to operate in a single mode. VCSEL structures that have utilized the oxide aperture have demonstrated record low threshold currents and voltages along with record power conversion efficiency [1].

## 2.6 Fluidic Self-Assembly

Fluidic self-assembly (FSA) of GaAs microstructures onto silicon substrates has been studied and attempted by several research groups [20] [21][24][25]. FSA offers the potential of mass integration of GaAs structures with Si substrates in a simple process. The problem with FSA is that it lacks precise control of placement of the devices. It has had limited success rates with VCSEL devices. Two approaches of FSA have been developed. The first relies mainly on gravitational forces for assembly with preferential assembly achieved through the shape of the devices and the receptor sites, while the second relies on capillary forces for self-assembly.

Figure 8 Oxidation rate dependence on a) AlAs mole fraction, b) layer thickness, c) temperature, and d) time [1].

Figure 9 Before and after oxidation for a lift-off VCSEL.

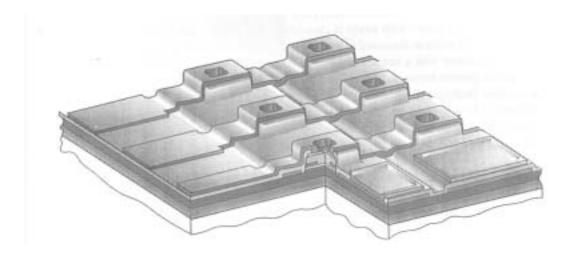

In the first approach, the FSA process begins by growing the VCSEL material and an underlying aluminum arsenide (AlAs) sacrificial layer on the GaAs substrate [21]. A metal layer is deposited on top of the VCSEL to form one of the contacts. Ion milling is used to etch the VCSEL structures down to the AlAs layer with 68° sidewalls [25]. The next step is to pattern the silicon substrate. A hole is created in the Si substrate to act as a receptor site for the VCSEL. A wet anisotropic etch is used to form the hole. Due to the arrangement of atoms in the silicon lattice, silicon can be etched in one crystal direction much faster than others. Ethylenediamine pyrocatechol etches silicon with greater than 100:1 selectivity over the {111} planes [25]. A trapezoidal hole can be formed with a 54.7° sidewall [17]. The next step is to release the VCSEL devices grown on the GaAs substrate. A buffered hydroflouric acid selective etch is used to remove the AlAs sacrificial layer, which frees the devices from the GaAs substrate [20]. The devices are then placed into a carrier fluid of either methanol or ethanol [25]. The fluid with the

devices is then dispersed over the silicon substrate. The trapezoidal shape of the device causes the VCSELs to preferentially fall with the small side down due to viscous forces. A metal ring is then deposited on top of the VCSEL to form the topside contact. Figure 10 demonstrates this process. Researchers at U. C. Berkeley have demonstrated successful fill rates of 70% when integrating VCSELs onto Si substrates [5].

Figure 10 FSA process for integration of GaAs VCSELs with a Si substrate.

While this method of FSA of VCSELs onto silicon substrates has relied on gravitational forces for assembly, capillary forces have been demonstrated to self-align larger devices using FSA [18]. With the MUMPs® process, angled sidewalls cannot be formed. Without the trapezoidal shape, the VCSELs will not preferentially fall with the correct orientation into the proper hole in the Si substrate. Success rates will then be substantially reduced. However, with chemical processing of the VCSEL and the silicon substrate, capillary forces can be used to self-align the VCSEL into holes in the Si substrate. A 100% success rate of structures with a radius of 50  $\mu$ m falling into specific areas onto a Si substrate through FSA has been achieved through capillary action [3].

Additional processing of the structures and the substrate introduces an attractive force between the receptor site and a surface of the device structure. The FSA technique utilizes hydrophobic (repelled by water)—hydrophilic (attracted to water) surface patterning and capillary forces of an adhesive liquid between binding sites to self-align the device [18]. The first step in the process is to deposit a gold layer onto both the device and the substrate. The gold is then patterned so that there is only gold on surfaces where bonding is desired. Gold is naturally hydrophilic as is the Si substrate [18]. However, by soaking the substrate with the patterned gold in ethanolic alkanethiol, a monolayer is formed on the gold patterns making the gold hydrophobic, while the Si substrate remains hydrophobic. Next, the substrate is passed through a film of a hydrocarbon-based liquid adhesive and then into water. The adhesive selectively coats the binding sites (gold regions) on the wafer. Only the substrate is lubricated so that the structures do not bond to themselves when suspended in the carrier fluid. The devices are then immersed into the water and directed toward the substrate with a pipette. After the gold hydrophobic regions of the microstructures come into contact with the adhesive coating, the

microdevices self-align due to interfacial free energy minimization between the surfaces [3]. The adhesive, polymerized at 80°C for half an hour permanently bonds the structures to the binding site [18]. Figure 11 illustrates the self-alignment process.

Figure 11 Self-alignment utilizing capillary forces

# 2.7 Wafer to Wafer Transfer

While FSA relies on removing the devices from the GaAs substrate and transferring them onto the Si wafer, other techniques have been developed that integrate the GaAs devices with the Si wafer by bonding the wafers together and then removing the GaAs substrate. By transferring the devices while still on the wafer, the concern that devices will fall correctly into place with a certain orientation is eliminated. One can precisely control the placement of the devices, however, the process is complicated by this critical alignment step. Both flip-chip bonding and epitaxial lift-off are wafer to wafer transfer techniques that use similar approaches.

In both techniques, the devices can be fabricated before (pre-processing) or after (post-processing) the epitaxial layer has been transferred to the other substrate [15]. The advantage with post-processing is that critical alignment between the wafers is not necessary. The wafers can be bonded together and the devices fabricated. In pre-processing the devices are fabricated and then the wafers must be precisely aligned, to ensure that the devices are placed properly onto

the Si wafer. The problem with post-processing is that metal surfaces are necessary for bonding. To fabricate matrix addressable arrays, each metal line must be electrically isolated. With post-processing, electrical isolation is not assured. Consequently, pre-processing is required and alignment cannot be avoided.

2.7.1 Flip-Chip Bonding. Flip-chip bonding (FCB) is a technique that has been used since the 1960's to integrate microelectronic components [7]. Recent work by a few groups has illustrated the effectiveness of this technique in integrating GaAs VCSELs with Si substrates. Prather has successfully flip-chip bonded an 8x8 individually addressable VCSEL array onto a CMOS driver [8]. Tuantranont et al. has also demonstrated the success flip-chip bonding. This group developed a MEMS/VCSEL hybrid system that integrates an individually addressable VCSEL array with a MEMS-controllable microlens array [22].

In the flip-chip bonding approach, a GaAs epitaxial layer is first grown on a GaAs substrate. The epitaxial layer contains an underlying etch stop layer or sacrificial layer, depending on the method of substrate removal. The epitaxial layer is then patterned and metal contacts are placed on both the epitaxial GaAs layer and on the Si substrate. Gold bumps (small balls of gold) are placed on the metal contacts of the substrate. The wafers are then aligned and bonded together using a bump bonder machine. After the wafers are bonded, the next step is to remove the excess substrate. This can be accomplished by grinding the wafer down using chemical mechanical polishing. Once most of the wafer has been removed, a chemical etch can be used to remove the remaining portion. The etchant will (or will virtually) cease etching once it reaches the etch stop layer. The other approach is to use a selective etchant that only erodes the sacrificial layer. Once the sacrificial layer is removed the GaAs substrate will come off. The devices will remain on the Si substrate. Figure 12 outlines the flip-chip process.

Figure 12 Flip-chip bonding of GaAs epitaxially grown VCSELs onto a Si substrate.

2.7.2 Epitaxial Lift-Off. Epitaxial lift-off (ELO) is another viable integration technique that has been successfully demonstrated by several research groups [5][15]. In the ELO process, devices are transferred from one substrate to another by removing a sacrificial epitaxial layer from the host wafer. Next, the remaining epitaxial layers are transferred to the target substrate. The ELO process allows for precise alignment of the devices because the devices are fixed on the epitaxial layer when they are transferred to the Si substrate.

The first step in the ELO process is to grow a thin film GaAs epitaxial layer and an underlying sacrificial AlAs layer on the GaAs host substrate [8]. The epitaxial layer can then be

processed along with the Si substrate to fabricate the devices and create the receptor sites. The epitaxial layer is then separated from the substrate by etching away the sacrificial layer. Since the epitaxial layer is very thin, it can suffer from strain and is extremely fragile. To eliminate or reduce the strain incurred and increase the mechanical strength, a layer of wax can be placed on top of the thin film heterostructures before the substrate is removed [5]. The thin film is then aligned and bonded to the Si substrate. After bonding the wax is removed

#### 2.8 MEMS

Micro-electro-mechanical systems (MEMS) are miniaturized electronic and mechanical components. Bulk micromachining, surface micromachining, and LIGA (Lithographie, Galvanoformung, Abformung) techniques are used to create these microstructures [4]. Bulk micromachining is processing that removes portions of the substrate while surface micromachining is processing on top of the substrate [11]. LIGA, meaning lithography, electroplating, and molding, is a micromachining process that is capable of yielding structures with high aspect ratios [11]. Mechanical devices such as beams, pits, gears, membranes and even motors have been fabricated using LIGA for a variety of applications that have mainly included sensors and actuators [4]. MEMS devices offer the obvious advantage of miniaturization, which saves space, energy, and weight, but they also have the potential to reduce cost since thousands of these devices can be fabricated on a single wafer. The ability to integrate micro-optical devices with MEMS structures offers many potential advantages. For example, it is possible to construct a MEMS-tunable VCSEL or place a VCSEL onto a polysilicon-MEMS micromirror and steer the VCSEL's beam output.

# 2.4 MUMPs®

The MUMPs<sup>®</sup> (Multi-User MEMS Processes) uses a three-layer polysilicon micromachining process to fabricate MEMS structures [9]. The foundry MUMPs<sup>®</sup> process uses a set growth sequence of silicon dioxide, polysilicon, and metal. The user designs the MEMS layer structures and sends the design to the MUMPs<sup>®</sup> foundry. The advantage of using MUMPs<sup>®</sup> is a reduction in cost since a foundry completes the fabrication from a user's design. The disadvantage is that the user is limited by the standard MUMPs<sup>®</sup> layer thickness and order of layers.

The MUMPs<sup>®</sup> process starts by using an n-type (100) oriented silicon wafer [9]. The process includes low-pressure chemical vapor deposition to deposit the subsequent polysilicon (poly) and silicon dioxide (oxide) layers. MUMPs<sup>®</sup> structures can have up to seven different layers including polysilicon (poly0, poly1, and poly2), silicon dioxide (oxide1 and oxide2), nitride, and gold (metal) [9]. Table 1 lists the different layers and their thicknesses.

The nitride layer acts as an electrical isolation barrier between a silicon substrate and the subsequent polysilicon layers. The oxides, which are actually phosphosilicate glass, are used as sacrificial layers. Various masks are used to pattern the different layers and a reactive ion etch is used to remove the unwanted layers. Table 2 lists the different etches and their optimum depths. The user, with a computer aided tool, specifies which different etches he/she wants and the precise location he/she wants the etch to be performed. By defining different lithography steps, various MEMS structures can be created through the MUMPs® process.

Table 1 MUMPs® Layers and Thickness [6]

| <u>Layer</u> | Thickness (µm) |  |

|--------------|----------------|--|

|              |                |  |

| Nitride      | 0.6            |  |

| Poly 0       | 0.5            |  |

| Oxide 1      | 2.0            |  |

| Poly 1       | 2.0            |  |

| Oxide 2      | 0.75           |  |

| Poly 2       | 1.5            |  |

| Metal        | 0.5            |  |

Table 2 MUMPs® Lithography Options [9]

| Layer to be etched | Lithography name | Depth (µm) |

|--------------------|------------------|------------|

| Oxide 1            | Dimple           | 0.75       |

| Oxide 1            | Anchor1          | 2.0        |

| Oxide 2            | Poly1-Poly2 Via  | 0.75       |

| Oxide 2            | Anchor 2         | 2.75       |

# 2.10 Summary

In this chapter, VCSEL structures and their operation were presented. An introduction to MEMS and the MUMPs® process was given. Matrix addressable and individually addressable VCSEL arrays were presented and compared. Finally, the integration of optical III-V devices with silicon MEMS was outlined by discussing the FSA, ELO, and FCB fabrication techniques.

# References

- 1. Bernhard, W. L. *Optical and Etching Studies of Native Aluminum Oxide Layers for Use in Microcavity Photonic Devices*. MS thesis, AFIT/GE/ENG/01M-01. School of Engineering and Management, AFIT (AU), Wright-Patterson AFB, OH. March 2001.

- 2. Bohringer, K. F., R. S. Fearing, K. Y. Goldberg, *Handbook of Industrial Robotics, 2nd Edition*. Wiley and Sons, 1998.

- 3. Böhringer, K. F., U. Srinivasan, R. T. Howe. "Modeling of Capillary Forces and Binding Sites for Fluidic Self-Assembly,"http://www.ee.washington.edu/faculty/karl/Publications/MEMS01-thara.pdf article from internet in October 2001.

- 4. Camporesi, L. "An Overview of the Applications of Microelectromachanical Devices", www.dig.bris.ac.uk/teaching/o a hf/lcamp.htm, article from internet on October 2001.

- 5. Ersen A., I. Schniter, E. Yablonovitch, T. Gmitter. "Direct Bonding of GaAs Films on Silicon Circuits by Epitaxial Liftoff," *Solid State Electronics*, vol 36, no. 12, pp1731-1739, 1993.

- 6. Hadley, M. A. Vertical-Cavity Surface-Emitting Laser Diodes: Design, Growth, Mode Control and Integration by Fluidic Self-Assembly. Dissertation, U. C. Berkeley, 1994.

- 7. Han, H., H. Chung, Y. Joe, S. Park, G. Joo, N. Hwang, M. Song. "The Application of Flip-Chip Bonding Interconnection Technique on the Module Assembly of 10 Gbps Laser Diode", *Journal of Electronic Materials*, vol. 27, no. 8, 1998.

- 8. Hargis, M. C., R. E. Carnahan, J. S. Brown, N. M. Jokerst. "Epitaxial Lift-Off GaAs/AlGaAs Metal-Semiconductor-Metal Photodetectors with Back Passivation", *IEEE Photonics Technology Letters*, vol 5, no. 10, October 1993.

- 9. Koester, D. A., Ramaswamy Mahadevan, Buzz Hardy, Karen W. Markus. *MUMPs Design Handbook Revision 5.0*, Research Triangle Park, NC: Cronos, 2000.

- 10. Koley, B., "8x8 Individually-Addressable VCSEL Driver Array for Flip-Chip Bonding with VCSEL Arrays," Paper written at the University of Maryland.

- 11. Kovacs, G. T. *Micromachined Transducers*. NY: McGraw Hill Publishing Co., 1998.

- 12. Lott J.A., "Photonics", OENG 775 Course Notes, Air Force Institute of Technology, Wright-Patterson AFB, Ohio, 45433-7765. June 2001.

- 13. Morgan, R.A., G. D. Guth, C. Zimmer, R. E. Leibenguth, M. W. Focht, J. M. Freund, K. G. Glogovsky, T Mullally, F. F. Judd, and M. T. Asom, "Two-Dimensional Matrix Addressed Vertical Caivty Top-Surface Emitting Laser Array Display," *IEEE Photonics Technology Letters*, vol. 6, no. 8, pp. 913-915, 1994.

- 14. Orenstein, M., A.C. Von Lehman, C. Chang-Hasnain, N. G. Stoffel, J. P. Harbison and L. T. Florez, "Matrix- Addressable Vertical Cavity Surface Emitting Laser Array," *Electronics Letters*, vol. 27, no. 5, pp. 70-71, 1991.

- 15. Pollentier, I., P. Demeester, A. Ackaert, L. Buydens, P.van Daele, R. Baets. "Epitaxial Lift-Off GaAs LEDs to Si for Fabrication of Opto-Electronic Integrated Circuits", *Electronics Letters*, vol. 26, no. 3, February 1990.

- 16. Prather, D. W. "Three-dimensional VLSI-Scale Interconnects", article taken from internet on September, 2001.

- 17. Srinivasan, U., M. Helmbrecht, C. Rembe, R. S. Muller, R. T. Howe. "Fluidic Self-Assembly of Micromirrors onto Surface Micromachined Actuators," http://bsac.eecs.berkeley.edu/~rembe/4A2-01.pdf article taken from internet in November 2001.

- 18. Srinivasan, U., D. Liepmann, R. T. Howe. "Microstructure to Substrate Self-Assembly Using Capillary Forces," *Journal of Microelectromechanical Systems*, vol. 10, no. 1, pp. 17-23, March 2001.

- 19. Sze, S. M., Semiconductor Devices, Physics and Technology. Murray Hill, N.J. 1985.

- 20. Talghader J. J., J. K. Tu, J. S. Smith. "Integration of Fluidically Self-Assembled Optoelectronic Devices Using a Silicon-Based Process," *Photonics Technology Letters*, vol. 7, no. 11, pp. 1321-1323, November 1995.

- 21. Tu, J. K., J. J. Talghader, M. A. Hadley, J. S. Smith. "Fluidic Self-Assembly of InGaAs Vertical Cavity Surface emitting Lasers onto Silicon," *Electronics Letters*, vol. 31, no.17, pp1448-1449, August 1995.

- 22. Tuantranont, A., V. M. Bright, J. Zhang, W. Zhang, J. Neff, Y. C. Lee. "MEMS Controllable Microlens Array for Beam Steering and Precision Alignment in Optical Interconnect Systems", *Technical Digest 2000 Sensor and Actuator Workshop*, pp. 101-104, June 4-8, 2000.

- 23. Ueki, N., H. Nakayama, J. Sakurai, A. Murakami, H. Otoma, Y. Miyamoto, M. Yamamoto, R. Ishii, M. Yoshikawa, T. Nakamura. "Complete Polarization Control of 12 x 8-Bit Matrix-Addressed Oxide-Confined Vertical-Cavity Surface-Emitting Laser Array," *The Japan Society of applied Physics*, part 2, no. 1, pp. L33-L35, January 2001.

- 24. Yeh, H. J., J. S. Smith. "Fluidic Self-Assembly of GaAs Microstructures on Si Substrates," *Sensors and Materials*, vol. 6, no. 6, pp. 319-331, April1994.

- 25. Yeh, H. J., J. S. Smith. "Fluidic Self-Assembly for the Integration of GaAs Light-Emitting Diodes on Si Substrates", *IEEE Photonics Tech. Letters*, vol. 6, no. 6, pp. 706-708, June 1994.

## 3. Design Methodology

#### 3.1 Introduction