#### Air Force Institute of Technology

#### **AFIT Scholar**

Theses and Dissertations

Student Graduate Works

3-2008

## Hardware Algorithm Implementation for Mission Specific **Processing**

Jason W. Shirley

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Hardware Systems Commons, and the Numerical Analysis and Computation Commons

#### **Recommended Citation**

Shirley, Jason W., "Hardware Algorithm Implementation for Mission Specific Processing" (2008). Theses and Dissertations. 2779.

https://scholar.afit.edu/etd/2779

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact AFIT.ENWL.Repository@us.af.mil.

## HARDWARE ALGORITHM IMPLEMENTATION FOR MISSION SPECIFIC PROCESSING

#### THESIS

Jason W. Shirley, Captain, USAF AFIT/GE/ENG/08-27

## DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

## AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

| ition of the United S | and do not reflect the artment of Defense, or |

|-----------------------|-----------------------------------------------|

|                       |                                               |

|                       |                                               |

|                       |                                               |

|                       |                                               |

|                       |                                               |

|                       |                                               |

|                       |                                               |

|                       |                                               |

|                       |                                               |

# HARDWARE ALGORITHM IMPLEMENTATION FOR MISSION SPECIFIC PROCESSING

#### **THESIS**

Presented to the Faculty

Department of Electrical and Computer Engineering

Graduate School of Engineering and Management

Air Force Institute of Technology

Air University

Air Education and Training Command

In Partial Fulfillment of the Requirements for the

Degree of Master of Science in Electrical Engineering

Jason W. Shirley, B.S.E.E.

Captain, USAF

March 2008

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

# HARDWARE ALGORITHM IMPLEMENTATION FOR MISSION SPECIFIC PROCESSING

Jason W. Shirley, B.S.E.E. Captain, USAF

#### Approved:

| /signed/                             | 27 Feb 2008 |

|--------------------------------------|-------------|

| Yong C. Kim, PhD (Chairman)          | date        |

| /signed/                             | 27 Feb 2008 |

| LaVern A. Starman, PhD, Maj (Member) | date        |

| /signed/                             | 27 Feb 2008 |

| Guna S. Seetharaman, PhD (Member)    | date        |

| /signed/                             | 27 Feb 2008 |

| Juan R. Vasquez, PhD (Member)        | date        |

#### Abstract

There is a need to expedite the process of designing military hardware to stay ahead of the adversary. The core of this project was to build reusable, synthesizeable libraries to make this a possibility. In order to build these libraries, Matlab® commands and functions, such as Conv2, Round, Floor, Pinv, etc., had to be converted into reusable VHDL modules. These modules make up reusable libraries for the Mission Specific Process (MSP) which will support AFRL/RY.

The MSP allows the VLSI design process to be completed in a mere matter of days or months using an FPGA or ASIC design, as opposed to the current way of developing a system which can take 1-2 years to complete. By having the libraries built, the components can be implemented in an FPGA or ASIC design over and over again. The libraries make it possible to make upgrades to weapons systems to meet the ever-changing needs the War Fighter faces. MSP makes it possible to develop various algorithms, including algorithms implemented in Matlab<sup>®</sup>. The MSP libraries were built and tested using TSMC 250-nm<sup>®</sup> technology library from the Taiwan Semiconductor Manufacturing Company. They were also synthesized for an FPGA. The modules were all synthesized using the CAD tools from Cadence<sup>®</sup> and Mentor Graphics<sup>®</sup>. Power, area, and delay results for each module were presented.

#### Acknowledgements

First and foremost, I would like to thank my Lord and Savior Jesus Christ for giving me the wisdom and knowledge to complete my thesis. I also owe a large debt of gratitude to my wife and daughter for their understanding and patience during my research at the Air Force Institute of Technology (AFIT). I would like to thank Dr. Yong Kim for his wisdom, knowledge, and helpfulness during my research as he guided and encouraged me throughout my research process. I would like to thank Dr. Juan Vasquez and Douglas Summers-Stay for sponsoring me, and I hope that the research that I have gathered is useful to the Air Force Research Lab (AFRL) AFRL/RY. Finally, I'd like to thank my fellow students for all of their encouragement and knowledge during my research efforts: Sam Stone, Benjamin Hancey, Eric Lam, James Crouch, and Gene Hockenberry.

Jason W. Shirley

## Table of Contents

|                                     | Page |

|-------------------------------------|------|

| Abstract                            | iv   |

| Acknowledgements                    | V    |

| List of Figures                     | ix   |

| List of Tables                      | xi   |

| List of Abbreviations               | xii  |

| I. Introduction                     | 1    |

| 1.1 Specific Issue                  | 4    |

| 1.2 Problem Statement               | 4    |

| 1.3 Scope and Assumptions           | 5    |

| 1.4 Thesis Organization             | 5    |

| II. Background                      | 7    |

| 2.1 Overview of VLSI Design Process | 7    |

| 2.2 VLSI Design Process             | 8    |

| 2.2.1 Specification                 | 9    |

| 2.2.2 Architecture                  | 9    |

| 2.2.3 RTL Coding                    | 11   |

| 2.2.4 RTL Verification              | 11   |

| 2.2.5 Synthesis/Manual Layout       | 11   |

| 2.2.6 Implementation/Fabrication    | 12   |

| 2.3 FPGA vs. ASIC Risk              | 13   |

| 2.4 MSP Design Reusability          | 14   |

| 2.5 Optical Flow                    | 17   |

| 2.6 Chapter Summary                 | 19   |

| III. Methodology                    | 20   |

| 3.1 Overall Design                  | 21   |

| 3.2 Two Dimensional Convolution     | 22   |

| 3.2.1 Memory                        | 23   |

| 3.2.2 Multiplier                    | 23   |

| 3.2.3 Control                       | 24   |

| 3.2.4 Multiplexer, Adder, Register  | 24   |

| 3.3 Matrix Transpose                | 25   |

|              |                                | Page |

|--------------|--------------------------------|------|

| 3.4          | Compute Derivatives            | 25   |

| 3.5          | Reduce Matrix Function         | 27   |

| 3.6          | Round/Floor                    | 28   |

| 3.7          | Pseudoinverse (Pinv)           | 28   |

| 3.8          | Synthesis/Timing               | 29   |

| 3.9          | Testing Procedure              | 30   |

| 3.10         | Chapter Summary                | 31   |

| IV. Analysis | s and Results                  | 32   |

| 4.1          | Overview of MSP Modules        | 32   |

| 4.2          | Error Analysis                 | 37   |

| 4.3          | Power, Area, and Delay         | 40   |

| 4.4          | Synthesis                      | 44   |

| 4.5          | Chapter Summary                | 50   |

| V. Conclus   | ions                           | 51   |

| 5.1          | Summary of the Project         | 51   |

| 5.2          | Future Work                    | 51   |

|              | 5.2.1 Improve Module Designs   | 52   |

|              | 5.2.2 Power, Area, and Delay   | 52   |

|              | 5.2.3 Complex Numbers          | 52   |

| Appendix A.  | Reducing Power Consumption     | 53   |

| A.1          | Clock Speed/Clock Gating       | 53   |

| A.2          | Turning Off The Circuit        | 54   |

| A.3          | Recycle Power                  | 55   |

| A.4          | Redesign Logic Of The Circuit  | 56   |

| A.5          | Higher Level of Integration    | 56   |

| A.6          | Dynamic Power Management       | 56   |

|              | A.6.1 Clock Gating             | 57   |

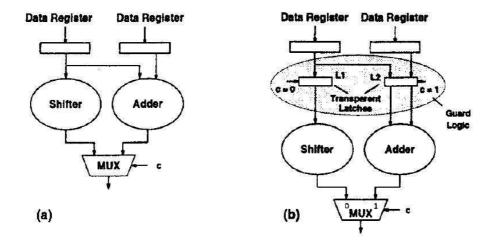

|              | A.6.2 Qualified System Latches | 58   |

|              | A.6.3 Guarded Evaluation       | 58   |

|              | A.6.4 Bus Deactivation         | 59   |

|              | A.6.5 Self-timed Techniques    | 59   |

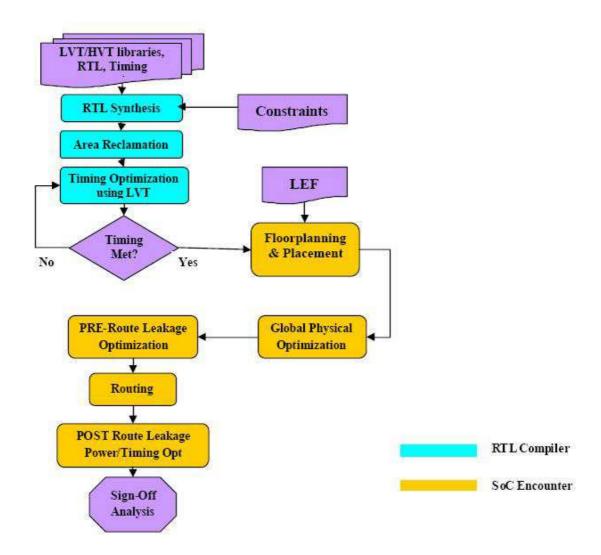

| A 7          | Synthesize                     | 59   |

|                |                                                        | Page |

|----------------|--------------------------------------------------------|------|

| Appendix B.    | Matlab® Code                                           | 61   |

| B.1            | HierarchicalLK                                         | 61   |

| B.2            | Reduce                                                 | 63   |

| B.3            | LucasKanade                                            | 63   |

| B.4            | LucasKanadeRefined                                     | 65   |

| B.5            | Expand                                                 | 67   |

| Appendix C.    | VHDL Code                                              | 69   |

| C.1            | Reduce Matrix Function Top-Level 1 Behavior Multiplier | 69   |

| C.2            | Reduce Matrix Function Top-Level 2 Behavior Multiplier | 75   |

| C.3            | Reduce Matrix Function Top-Level 1 Booth Multiplier .  | 85   |

| C.4            | Reduce Matrix Function Top-Level 2 Booth Multiplier .  | 91   |

| C.5            | Compute Derivatives Fx using Booth Multiplier          | 102  |

| C.6            | Compute Derivatives Fy using Booth Multiplier          | 107  |

| C.7            | Compute Derivatives Ft using Booth Multiplier          | 111  |

| C.8            | Matrix Transpose                                       | 116  |

| C.9            | Pseudoinverse                                          | 119  |

| Bibliography . |                                                        | 127  |

| Vita           |                                                        | 128  |

## List of Figures

| Figure |                                                                          | Page |

|--------|--------------------------------------------------------------------------|------|

| 1.1.   | Power, Area, and Delay Triangle                                          | 2    |

| 1.2.   | A Sample of Target Tracking Imagery                                      | 5    |

| 2.1.   | Three Main Steps for VLSI Design Process                                 | 7    |

| 2.2.   | Six Steps for VLSI Design Process                                        | 8    |

| 2.3.   | Nand Gate Layout                                                         | 12   |

| 2.4.   | Standard Design Time vs. MSP Design Time                                 | 15   |

| 2.5.   | Optical Flow Vectors for a $250 \times 400$ Image                        | 18   |

| 4.1.   | Reduce Matrix Function Top Level Design 1                                | 32   |

| 4.2.   | Conv2 Sub-Modules Design                                                 | 33   |

| 4.3.   | Behavior Multiplier Module Design                                        | 33   |

| 4.4.   | Booth Multiplier Module Design                                           | 34   |

| 4.5.   | Reduce Matrix Function Top Level Design 2                                | 34   |

| 4.6.   | Multiplier State Machine Design                                          | 35   |

| 4.7.   | Booth Multiplier State Machine Design                                    | 35   |

| 4.8.   | Compute Derivatives Top-Level Design                                     | 36   |

| 4.9.   | Matrix Transpose Top-Level Design                                        | 36   |

| 4.10.  | Pseudoinverse Top-Level Design                                           | 37   |

| 4.11.  | Reduce Matrix Function ${\tt Matlab^{\circledR}}$ vs. VHDL Percent Error | 38   |

| 4.12.  | Reduce Matrix Function Module Net Power(mW) vs. Clock Speed              | 40   |

| 4.13.  | Reduce Matrix Function Module Cell Area vs. Clock Speed $$               | 41   |

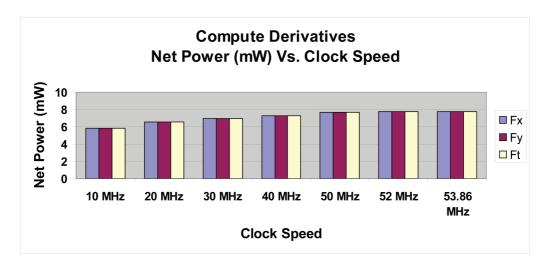

| 4.14.  | Compute Derivatives Module Net Power(mW) vs. Clock Speed                 | 41   |

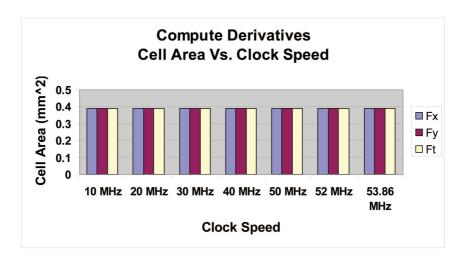

| 4.15.  | Compute Derivatives Module Cell Area vs. Clock Speed                     | 42   |

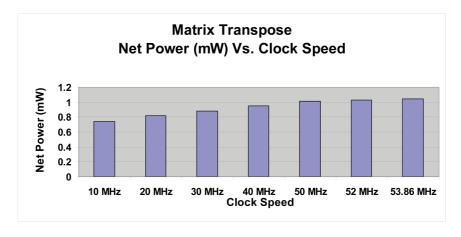

| 4.16.  | Matrix Transpose Module Net Power(mW) vs. Clock Speed $$                 | 42   |

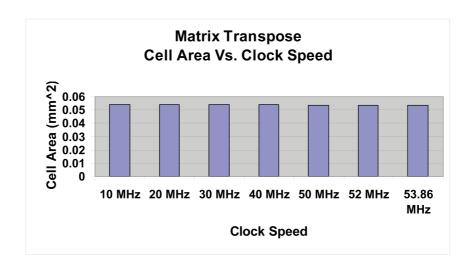

| 4.17.  | Matrix Transpose Module Cell Area vs. Clock Speed                        | 43   |

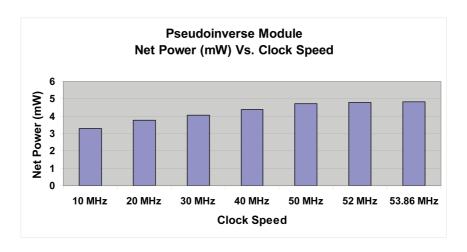

| 4 18   | Pseudoinverse Module Net Power(mW) vs. Clock Speed                       | 43   |

| Figure |                                                      | Page |

|--------|------------------------------------------------------|------|

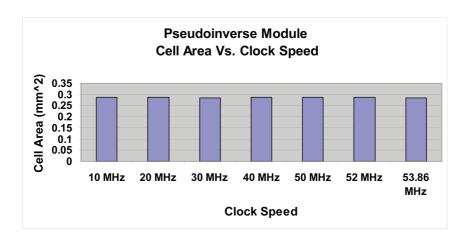

| 4.19.  | Pseudoinverse Module Cell Area vs. Clock Speed       | 44   |

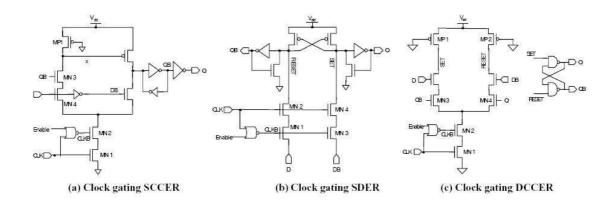

| A.1.   | Energy Recovery Clocked Flip-Flops with Clock Gating | 54   |

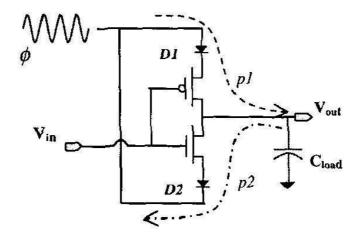

| A.2.   | Clock Recovery Circuit                               | 55   |

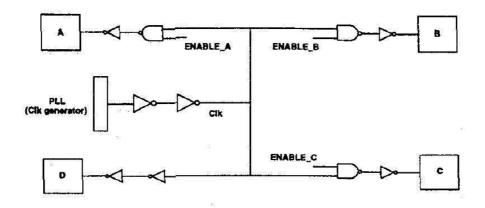

| A.3.   | Illustration of Clock Gating                         | 57   |

| A.4.   | Guarded Evaluation                                   | 58   |

| A.5.   | Leakage Power Optimization Flow                      | 60   |

## List of Tables

| Table |                                                                              | Page |

|-------|------------------------------------------------------------------------------|------|

| 2.1.  | Summary of Maximum Clock Frequency for Modules                               | 16   |

| 3.1.  | Configurable parameters                                                      | 21   |

| 4.1.  | Comparison between ${\tt Matlab}^{\circledR}$ and VHDL Gaussian Distribution | 38   |

| 4.2.  | Comparison between ${\tt Matlab}^{\circledR}$ and VHDL Pseudoinverse Module  | 39   |

| 4.3.  | FPGA Synthesize Results for Top-Level 1, Behavior Multiplier                 | 45   |

| 4.4.  | FPGA Synthesize Results for Top-Level 2, Behavior Multiplier                 | 45   |

| 4.5.  | FPGA Synthesize Results for Top-Level 1, Booth Multiplier                    | 46   |

| 4.6.  | FPGA Synthesize Results for Top-Level 2, Booth Multiplier                    | 46   |

| 4.7.  | ${\it FPGA}$ Synthesize Results for Compute Derivative Fx Module .           | 47   |

| 4.8.  | FPGA Synthesize Results for Compute Derivative Fy Module .                   | 47   |

| 4.9.  | FPGA Synthesize Results for Compute Derivative Ft Module .                   | 47   |

| 4.10. | FPGA Synthesize Results for Matrix Transpose Module                          | 48   |

| 4.11. | FPGA Synthesize Results for Floor Module                                     | 48   |

| 4.12. | FPGA Synthesize Results for Round Module                                     | 49   |

| 4.13. | FPGA Synthesize Results for Pseudoinverse Module                             | 49   |

| 4.14. | Summary of Maximum Clock Speed for Modules                                   | 49   |

| 4.15. | Summary of Net Power Watts for Modules                                       | 50   |

## List of Abbreviations

| Abbreviation |                                            | Page |

|--------------|--------------------------------------------|------|

| AFIT         | Air Force Institute of Technology          | V    |

| AFRL         | Air Force Research Lab                     | V    |

| VLSI         | Very Large-Scale Integration               | 1    |

| MSP          | Mission Specific Process                   | 1    |

| VHDL         | VHSIC Hardware Description Language        | 1    |

| FPGA         | Field Programmable Gate Array              | 3    |

| ASIC         | Application Specific Integrated Circuits   | 3    |

| TSMC         | Taiwan Semiconductor Manufacturing Company | 4    |

| Conv2        | Two Dimensional Convolution                | 4    |

| Pinv         | Pseudoinverse                              | 4    |

| RTL          | Register Transfer Level                    | 5    |

| DoD          | Department of Defense                      | 11   |

| SRAM         | Static Random Access Memory                | 13   |

| CLB          | Configurable Logic Block                   | 44   |

| DSP          | Digital Signal Process                     | 52   |

| DPM          | Dynamic Power Management                   | 54   |

| DC           | Direct Current                             | 55   |

| AC           | Alternating Current                        | 55   |

| Vp           | Peak Voltage                               | 55   |

| Vth          | Threshold Voltage                          | 56   |

| P            | Power                                      | 56   |

| V            | Voltage                                    | 56   |

| I            | Current                                    | 56   |

## HARDWARE ALGORITHM IMPLEMENTATION FOR

#### MISSION SPECIFIC PROCESSING

#### I. Introduction

In today's advancing technologies, devices are shrinking and densities of integrations are increasing. With these trends come many new challenges in designing integrated electronic circuits and systems. To achieve high performance (Power, Speed, Dynamic Range, etc.) in new integrated circuits for next-generation systems; new methodologies must be created, adopted, and executed.

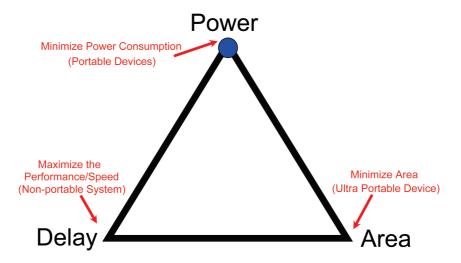

The objective of this research is to examine and investigate current difficulties/problems associated with modeling and fabricating Very Large-Scale Integration (VLSI) circuits, then provide reusable library cells for AFRL/RY directorate's Mission Specific Process (MSP) in Very High Speed Integrated Circuit (VHSIC) Hardware Description Language (VHDL). These reusable libraries can be broken into three variations which are as follows: optimizing power, minimizing area, and minimizing delay. By having these libraries built and ready to go, system requirements can be upgraded and changed in a matter of days instead of months or even years. These reusable libraries make it possible to meet the changing requirements of the operational environment. The MSP makes it flexible for system changes to be implemented quickly into a system. The variations between power, area, and delay can be generalized as the points on an equilateral triangle as seen in Figure 1.1. The points of the triangle represent the priority optimal design for the given circuit. For example, if you want to optimize the power, the other two parameters will not be the priority. This will cause the design to have minimal power consumption at the expense of the final de-

Figure 1.1: Power, Area, and Delay Triangle.

sign being large or slow. The blue dot in the triangle represents where the priority lies, meeting design specifications.

The idea behind AFRL/RY directorate's MSP is a threefold approach to designing circuits. First, it takes time for the design to be developed and fabricated before it can get into the hands of the customer. The design to market can take up to 1-2 years depending on the technology and the level of difficultly of the circuit design. In addition to the amount of time it takes to develop the product, it can be obsolete in only a few years. This is what makes MSP so unique; it is made up of pre-built synthesizable reusable libraries so the designer doesn't have to start from scratch. The designer can quickly use the pre-built libraries and make new ones when specifications change and add them to the library.

Second, if modifications are required for additional features to be added to the product, then you have to wait for the redesign to take place. You have to pay the vendor again for the changes they make and wait for the new design to be delivered. This is where MSP comes in to reduce the cost and schedule of redesigning a circuit just to make a few changes for additional specifications. The use of the reusable libraries makes designing a circuit much easier than current methodologies. In a

sense, it is like putting a Lego®set together. By having all the pre-built parts it's just a matter of integrating them together for your personal application.

Thirdly, a Field Programmable Gate Array (FPGA) can replace an Application Specific Integrated Circuit (ASIC) design, unless you want absolute performance. The use of MSP makes it flexible for the designer to develop prototypes faster and cheaper for an FPGA as opposed to an ASIC design. Having MSP in your tool box can save time and money for the next generation of a circuit design. Therefore, the War Fighter will have new equipment in the field in a matter of days as opposed to the old way of doing business, which could take 1-2 years for a weapons system to be developed.

This project will support AFRL/RY in their development of a target tracking project, where the circuits and digital circuits are to be implemented in one chip. The goals are to provide reliable building blocks as portable synthesizable reusable libraries. These libraries will enable the War Fighter to get an upgradable weapon system in a matter of a few days or hours and to keep up-to-date with the everchanging Global War on Terrorism.

Building these reusable libraries and making them usable for FPGA or ASIC designs is beneficial in many ways. For instance, programming the design on an FPGA makes it possible to protect the design against enemy hands. Anti-tamper methods on the FPGA board protects the design from being discovered by the enemy. Additionally, placing the designs on an FPGA allows the weapons system to be implemented quicker than sending the design to a foundry for fabrication as an ASIC design, which can take months due to long lead times that the foundries put in their schedule. Once the design is created on an ASIC chip it has to be thoroughly tested to find faults in the fabrication process. All these design steps take time, especially if there are problems with the completed design.

#### 1.1 Specific Issue

The War on Terrorism has made the military solider depend on today's technology of global positioning systems, radar systems, and different communication devices. These devices, being mobile or not, are required for them to operate in the field and communicate with Command and Control. For this reason it is essential that these libraries be built and perfected.

With any circuit design there are three key parmeters that designers face when designing circuits, and they are as follows: power, area, and delay. The designer has to make tradeoffs between these three parmeters to meet their specific design constraints. Every commercial or military application has its own specifications for power, area, and delay.

The VLSI technology continues to place more and more transistors on a single chip. This allows the chips to become more powerful in computing power as the area of the chips remain small. The chips constantly require electrical power to keep them operational which makes it difficult for the War Fighter to do their mission without wondering if their batteries are going to sustain throughout their mission. There is a need to be able to run longer missions and have longer lasting equipment that doesn't require battery change-outs in the middle of a critical mission. This low power optimization will be using a 250-nm technology library [15] from the Taiwan Semiconductor Manufacturing Company (TSMC). This library will provide a starting point to develop circuits that have lower power consumption for the future.

#### 1.2 Problem Statement

The problem is to take the AFRL/RY Optical Flow Dense Algorithm written in Matlab<sup>®</sup> and convert the commands into synthesizable reusable library modules written in VHDL. We will be laying the foundation with these synthesizable reusable libraries for other weapons systems that require Matlab<sup>®</sup> commands such as, Round, Floor, Two Dimensional Convolution (Conv2), and Pseudoinverse (Pinv), etc. The

Figure 1.2: A Sample of Target Tracking Imagery [1].

Optical Flow Dense Algorithm can provide various libraries to handle Unmanned Aerial Vehicles for image processing. An example of target tracking imagery can be seen in [1] Figure 1.2. The small rectangles show targets that can potentially be tracked using Optical Flow.

#### 1.3 Scope and Assumptions

It is assumed that the reader has knowledge about the VLSI technology and understands VHDL, scripting, and intergrating the script in Cadence®software program or Modelsim®. The main software programs that will be used for this research are Modelsim®, Mentor Graphics®, and Cadence®Companies' software tools. The simulations will be run on Modelsim®to verify the Register Transfer Level(RTL) coding. Cadence®and Mentor Graphics®software tools will be used to verify that the modules are synthesizable.

#### 1.4 Thesis Organization

Chapter 2 of this thesis will give background information required to understand the technology options that are available for use to reduce power consumption. Each option will be briefly explained and the main focus of the research project option will be expounded into further details and discussions. Also, background information will be given to support the design decisions used in Chapter 3. Chapter 3 will discuss the theory and methods that were used for this thesis project. Chapter 4 will look at the results that were gathered throughout this research and will be analyzed and discussed. Finally, Chapter 5 will discuss future work and topics. The Modelsim®VHDL code will be located in Appendix C.

#### II. Background

This chapter will give an overview of the background information used throughout this research. The MSP idea makes it flexible enough to accommodate the everchanging Air Force missions. This section will present an overview of the VLSI Design Process as well as a more in depth view of the process. We will also discuss FPGA vs. ASIC Risk, MSP Design Reusability, and Optical Flow.

#### 2.1 Overview of VLSI Design Process

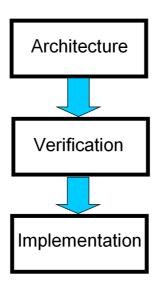

The VLSI Design Process can be summed up in the following three main steps: architecture, verification, and implementation and can be seen in Figure 2.1. The architecture is made up of three methods to design a circuit which are power, area, and delay (speed). Each architecture has it pros and cons for design implementation depending on what you are trying to achieve. The use of the circuit will drive what architecture you should use when designing it.

It is important to verify that your expected results match your simulated results. Once you have determined your design is working properly through simulations it is time to implement your design on an FPGA or fabricated circuit such as an ASIC.

Figure 2.1: Three Main Steps for VLSI Design Process

Figure 2.2: Six Steps for VLSI Design Process

The fabrication process for a circuit can take anywhere from 3 to 6 months at the foundry. In the next section, the VLSI Design Process will be broken down for a more magnified look at the steps involved to build an operational design.

#### 2.2 VLSI Design Process

The typical VLSI Design Process can be broken into the following six steps and can be seen in Figure 2.2:

- 1. Specification

- 2. Architecture

- 3. RTL Coding

- 4. RTL Verification

- 5. Synthesis

- 6. Implementation/Fabrication

Each of these steps will be discussed further for an understanding of what is required before a design can be implemented into the field as an operational weapons system.

- 2.2.1 Specification. The specification for any design comes from the customer who has a specific need for a project they want built and implemented. There are three different design strategies for circuits custom, ASIC, and FPGA. The customer lists the criteria they want for their system, which could be a specific size (area) of the circuit, a certain power usage, or delay (speed) of the design, or even that they want the design written in VHDL. The vendor (designer) will discuss with the customer the possibilities based on the technology available at the time the original specification was created.

- 2.2.2 Architecture. There are three different architectures that can be implemented in any design. The three architectures are power, area, and delay (speed).

- 2.2.2.1 Power. Clock control plays a major role when designing a circuit to reduce power consumption. Reducing the speed of the clock for a circuit will reduce the switching activity. This results in power savings by limiting the amount of switching activity that takes place. Besides reducing the speed of the clock for the circuit, designers have also proposed "clock gating [13] by modifying the design of the existing energy recovery clocked flip-flops to incorporate a power saving feature that eliminates any energy loss on the internal clock and other nodes of the flip-flops." According, to Steve Kilts, in his book, Advanced FPGA Design, he suggests the following:

The most effective and widely used technique for lowering the dynamic power dissipation in synchronous digital circuits is to dynamically disable the clock in specific regions that do not need to be active at particular stages in the data flow [9].

It would be ideal to have the circuit temporarily turn the clock off when a particular section of the circuit is not required to reduce power consumption. These are a few techniques that are available for use to reduce power consumption. Additional power reduction techniques can be found in Appendix A.

2.2.2.2 Area. Another architecture that can be used when developing a circuit design is area. Ways to implement reduction in area for a circuit depends on picking the correct topology. Topology that focus on reducing the area size of a circuit can be attained by reusing [9] "the logic resources to the greatest extent possible, often at the expense of throughput(speed)." When you want to increase the delay for a design you need to pipeline your design. However, to reduce the area you need to do the opposite of creating pipelines, you need to roll them up to be able to use the available resources. Also, it is a good idea, according to Steve Kilts, to [9] "share logic resources between different functional operations."

2.2.2.3 Delay (Speed). The third architecture that can be used when designing a circuit is speed. There are three ways to describe speed in regards to circuit design - they are throughput, latency, and timing. In the book Advanced FPGA Design [9], Kilts gives a description for each one of these.

A high-throughput design is one that is concerned with the steady-state data rate but less concerned about the time any specific piece of data requires to propagate through the design (latency). A low-latency design is one that passes the data from the input to the output as quickly as possible by minimizing processing delays. Timing refers to the clock speed of a design. The maximum delay between any two sequential elements in a design will determine the max clock speed [9].

A key factor that should be considered when designing a circuit for speed is to use pipelining wherever possible to increase your throughput. The idea of pipelining is very similar to how an assembly line works. Each member is continually performing their specific task; they finish one, pass it on to the next station, and get another. The result is that a completed product is continuously produced. Pipelining [9] is a way to increase throughput for a process. Another [9] technique is to have the system run things in parallel to speed up the process. This technique is most useful when doing math calculations in a design.

2.2.3 RTL Coding. The third step in the VLSI Design Process is RTL Coding. RTL Coding is nothing more than what language you will code your design in. There are different Hardware Description Languages (HDL) that can be used to make an RTL module. The most commonly used RTL modeling languages are the following:

- 1. VHDL

- 2. Verilog

- 3. System Verilog

VHDL is the adapted hardware description languages for the Department of Defense (DoD). For this thesis we will code our design in VHDL.

2.2.4 RTL Verification. Step four in the VLSI Design Process is RTL Verification. RTL Verification is when you verify that your VHDL code simulates correctly. The simulation waveform generated in Modelsim®gives you a waveform to show the circuit is functioning. If this waveform gives you the expected results then your code and RTL are working properly.

2.2.5 Synthesis/Manual Layout. A flexible synthesis tool, such as Leonardo Spectrum by Mentor Graphics®Tool, allows a synthesizable HDL design to be synthesized for both FPGA and ASIC. The software tool uses optimization algorithms to determine the best floor design, place, and route of the design. The synthesis step has made it possible for an FPGA to only need the design to be download to the FPGA board to verify whether the simulation results match the synthesis results and meet the specifications that were stated at the beginning of the VLSI Design Process. Unlike the FPGA design, after the ASIC design is synthesized, it still needs to be sent to a foundry to be fabricated. The use of FPGA eliminates the fabrication step, it is economically inexpensive to own and can be reconfigured for a new design in a matter of seconds, depending on the size of the design. Therefore, if there was a problem with the timing of the design and it didn't meet the specifications of the design, the

Figure 2.3: Nand Gate Layout

designer would be aware of the problem and begin to correct the timing issue. However, the ASIC design wouldn't find this problem until the design was tested after it was received from the foundry.

When developing a custom design, a manual layout could be used. This would require you to hand place every piece of the circuit in a location that is determined by you. Then you would have to route all the cell wires together. This is a very tedious and time consuming process. The designer has to worry about design rule violations such as placing the cells too close together or too far apart causing timing delays. An example of a handmade design of a Nand Gate is seen in Figure 2.3. This Nand Gate is only one gate. If you have a complicated design, in the range of hundreds of millions of gates, you can see how this task can be extremely time consuming. Once the gates have been layed out, then you have to determine if they are in the optimal position for the place and route step. This design lacks scalability when new technologies are created, the old layout may not be usable at all in ASICs. However, ASIC designs will have a higher absolute performance than FPGA designs.

2.2.6 Implementation/Fabrication. Implementation/Fabrication is the final step in the VLSI Design Process. Implementation/Fabrication consists of the design being synthesized for an ASIC design, otherwise it would be a manual layout design. The design is finalized and the circuit is sent on as a computer file to the foundry for

the fabrication process. At the foundry, several different metal layers and polysilicon layers will be used to create the design. The design will also need a set of test vectors to be sent with it to the foundry. This is required to determine if the design is working correctly. If the design comes back correct, then this ASIC or custom design can only be used for this given application. On the other hand, if the design comes back not working properly, then the designer will have to analyze the circuit and determine where in the six step process the design failed. This basically leaves the designer at square one. All of this time has been invested into a product that does not work. Even if the change is found within a few days it will still be 3 to 6 months from the time they send it to the foundry before they will see it again. Therefore, making an ASIC design is very costly and time consuming for the design process. Unlike the ASIC, the FPGA can be designed and implemented in an shorter time span and is an economical, reusable, and reconfiguable product.

#### 2.3 FPGA vs. ASIC Risk

Now that the VLSI design cycle has been thoroughly discussed, let us examine the risk that is involved with building a circuit to meet an FPGA or ASIC design. The FPGA is an inexpensive design option that will only cost a few thousand dollars for a board. The Static Random Access Memory (SRAM) FPGA is reconfigurable in that once you put one design on the board you can take the program off the board and reprogram the board for a completely new design with no new costs involved. Once the design is synthesizable and thoroughly tested, it requires less time to become operational. There is also a higher chance that your FPGA design will synthesize and work the first time, unlike the ASIC design, saving a company time and money. On the other hand, an ASIC design is an expensive investment and will require substantially more time and money to be implemented. For example, let us say that a company is implementing a new design and they choose to take the route of an ASIC design. They could invest a million dollars into the program before it is even fabricated due to the labor intensive effort required. If the design fails once, it comes back from fabrication

to engineers who will thoroughly look at the design to understand why it failed. Once the failure has been determined, it may cost an additional \$100,000 from the time the engineers determine the problem to the time it is refabricated and works. Also, this design can only be used for this single application. If this application was for a satellite that was in space and it failed, the satellite would lose that functionality in the system. However, if the design was on an FPGA, the design could be reprogrammed in a matter of minutes to keep the system functioning. As you can see, there are several risks that need to be considered when deciding what design solution to use. In this thesis, we will create a set of synthesizable VHDL libraries targeting FPGAs and ASICs. However, we are putting emphasis on the FPGAs due to extra time and cost required for us to fabricate ASIC solutions for validation purposes.

#### 2.4 MSP Design Reusability

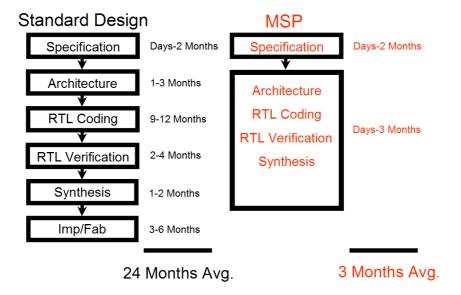

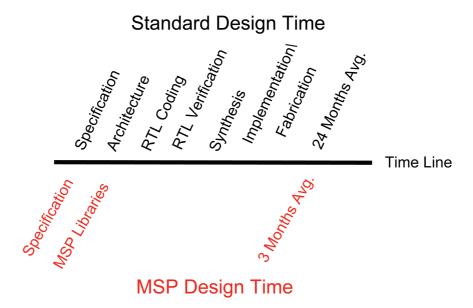

Now you have seen the design steps required for a VLSI circuit design and how there are two different approaches to reach a solution. MSP offers design reusability by creating multiple modules of the same functioning task that focus on optimizing power, area, and delay modules. A typical design takes an average of 24 months to complete. The MSP design can take 3 months on average to complete, due to the synthesizable reusable libraries. Each design is unique to itself with different variables that depend on the length of time required to complete a design. Some of the variables that need to be considered are as follows: complexity factor, can you reuse anything from a previous design, is the task fully defined, experience of the designer, etc. A typical design timeline can be seen in Figure 2.4. The MSP libraries include the Architecture, RTL Coding, RTL Verification, and Synthesis. Using these MSP libraries can save time, money, and resources when designing a circuit. Chang and Aguan [3] state how important it is to have reusable VHDL modules in their journal article "Design-for-reusability" in VHDL.

Figure 2.4: Standard Design Time vs. MSP Design Time

The reuse of electronic components can improve productivity in system design. However, without careful planning, components are rarely designed for reuse.

There is also more than one option when designing a multiplier, adder, or controller. You can build a behavior combinational multiplier, structurally combinational multiplier, behavior sequential multiplier, structurally sequential multiplier, or even a Booth multiplier just to name a few. They all have strengths and weaknesses for a design. The MSP idea is to build reusable libraries to meet the needs of the designers. A multiplier is a good example of this. The designer can build three variations of a multiplier to have one optimized for power, one for area, and one for delay (speed). When a new requirement is generated and it requires the use of a multiplier, the reusable libraries of power, area, and delay will be available. Since these modules have already been optimized, there is no additional work for the designer. This concept goes back to the the power, area, and delay triangle that was shown in Figure 1.1. The pre-built modules make it possible for the designer to only have to choose which module will work best for the specifications they were given. This can be seen in Table 2.1 where there are four types of multiplier designs showing their results for power, area, and delay. These results came from the software tool Cadence<sup>®</sup>. The

Table 2.1: Summary of Maximum Clock Frequency for Modules

| Type of Multiplier       | Power mW | Area mm <sup>2</sup> | Max. Freq. MHz | Constrained |

|--------------------------|----------|----------------------|----------------|-------------|

| Booth                    | 37.17    | 0.1537               | 53.99          | Yes         |

| Combinational Behavior   | 7.35     | 0.2043               | 53.09          | No          |

| Combinational Structural | 9.13     | 0.2422               | 28.23          | No          |

| Sequential Behavior      | 64.87    | 0.2151               | 37.31          | Yes         |

constrained column in the table gives a clear picture of what power, area, and maximum clock frequency can be achieved. When combinational designs are synthesized in Cadence®there is no clock used to determine how fast the design will run accurately. Therefore, Cadence®gives a best guess estimate for the power, area, and delay. As you can see, the Booth Multiplier has the fastest delay but the third largest amount of power consumption. One multiplier design may have the smallest area, but the slowest delay. It is up to the designer to pick which module will work best for their application.

If you take this a step further and expand to other modules like adders, subtractors, and controllers, you will have generated an arsenal of modules that have been optimized for power, area, and delay. This will be like picking out a new car. What options do you want for a new car - power windows, cd player, full size spare tire, etc.? Having these libraries built, reconfigurable, and reusable makes designing a weapon system simpler and saves time, money, and resources. Also, using an FPGA makes it easier to upgrade the system at a lower cost while applying less time. There will be several different variations of the same module focusing on optimized power, area, and delay. For example, if a design calls for fast multiplications to be performed, the designer has the option to choose the multiplier that has been optimized for speed from the reusable libraries that are already built.

In this thesis we will be implementing a Booth multiplier. The Booth multiplier is based on adding, subtracting, and shifting the binary values several times. Andrew Booth [5] noticed this can be achieved by having a lookup table to determine if the binary value needs to be added, subtracted, or do no operation and only shift the

binary values one place. The Booth algorithm is summarized in points 1-3 below [5]. By using a lookup table, it is possible to quickly determine what operation needs to be performed. The best thing about the Booth multiplier is the option it has to perform no operation if there is a run of "00" or "11" in the number being multiplied. This do nothing option reduces the number of operations, saving clock cycles required to compute the multiplication. For example, if the bit width is 32 bits, it will only require 16 clock cycles to complete the multiplication. For this thesis we will implement a 2 bit shift Booth multiplier to cut the clock cycles in half from the given number of input bits.

Booth Multiplier Algorithm Summary:

1. Examine each pair of digits in the multiplier, creating the first pair by appending a dummy '0' at the least significant end.

If the pair is 01, add the multiplicand.

If the pair is 10, subtract the multiplicand.

Otherwise, do nothing.

- 2. Shift both partial product and multiplier one place to the right, allowing the next pair of digits to be examined.

- 3. Repeat as many times as there are digits in the multiplier [5].

#### 2.5 Optical Flow

The Optical Flow algorithm compares two images together to see what is different between the two images. Some applications where optical flow are used are change detection, computer vision, pattern recognition, tracking targets, and image processing. Optical Flow is best described by Horn and Schunck [7] in their paper, "Determining Optical Flow."

Optical flow is the distribution of apparent velocities of movement of brightness patterns in an image. Optical flow can arise from relative mo-

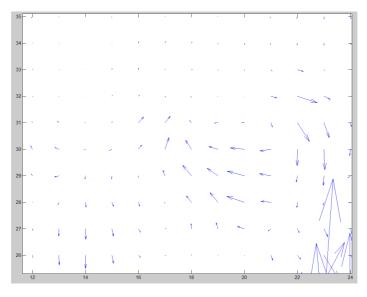

Figure 2.5: Optical Flow Vectors for a  $250 \times 400$  Image

tion of objects and the viewer. Consequently, optical flow can give important information about the spatial arrangement of the objects viewed and the rate of change of this arrangement.

There are two [7] [10] well regarded methods for calculating optical flow - are Horn-Schunck and Lucas-Kanade methods. The Horn-Schunck [7] method looks at the difference between the brightness and contrasts between the two images to estimate what changes have occurred. The changes are represented in a vector field to show the direction of motion the image is moving compared to the first image. The Lucas-Kanade method [10] makes use of the "spatial intensity gradient of the images." Using the Horn-Schunck or the Lucas-Kanade method requires large amounts of calculations to determine if there is a change between the first image and the second image. In this project, we will look at the Lucas-Kanade method to determine an optical flow solution between two images. An example of a vector field that was produced between two images using the Lucas-Kanade method is shown in Figure 2.5. These results were attained from Matlab® comparing two images that are 250 × 400 pixels.

#### 2.6 Chapter Summary

The background information for Chapter 2 covered the following: VLSI Design Process, FPGA vs. ASIC Risk, MSP Design Reusability, and Optical Flow. Several low power, area, and delay (speed) implementations were also looked at and discussed in the architecture section of the VLSI Design Flow section. MSP has shown the importance of creating many different modules for optimized power, area, and delay that will perform the same task. Two different methods to perform Optical Flow have been discussed, which were the Lucas-Kanade and Horn-Schunck Optical Flow methods. We will build reusable libraries in VHDL for the Lucas-Kanade method so the libraries can later build a complete Lucas-Kanade Optical Flow system. This image processing can be used in part of the target tracking project. These ideas will be discussed further in Chapter 3 to develop this thesis project.

#### III. Methodology

The methodology used to convert the Matlab® commands that generated the Dense Optical Flow will be discussed in this chapter. The research goal is to convert the Matlab® commands, located in Appendix B, used in the Dense Optical Flow to build reusable VHDL libraries such as, Conv2, Matrix Transpose, Round, Floor, and Pinv, etc. The goal is to demonstrate functioning MSP modules that are reusable for image processing such as Optical Flow, DSP, computer vision, pattern recognition, tracking targets, change detection, etc. These MSP libraries will be the key for the foundation of these applications.

The Dense Optical Flow Matlab® command functions will be created and demonstrated using smaller modules. These modules will make up the parts for the Matlab® command that can later be used to build an Optical Flow system using MSP modules. An example of some of the Matlab® commands that are used in Optical Flow code can be seen in Listing III.1.

#### Listing III.1:

```

1 % Example of using the conv2 command

2 hResult = conv2(im, mask);

3

4 % Example of using the matrix transpose command

5 curFx = curFx';

6

7 % Example of using the Pinv command

8 U = pinv(A'*A)*A'*curFt;

9

10 % Example of using the round command

11 uIn = round(uIn);

12

13 % Example of using the floor command

14 halfWindow = floor(windowSize/2);

```

To create these commands, smaller modules were designed around the Matlab® Dense Optical Flow written by Sohaib Khan [8] using the Lucas-Kanade algorithm [10].

The reason for creating individual modules and making them configurable components is to be able to use a generic module and shape it to meet the needs of a specific design. We will assume that the image sizes will not change while the data is being recorded with a camera and the modules will be set to receive grayscale images. This parameter is configurable to meet future needs. The configurability parameters of many of the individual modules can be seen in Table 3.1.

Table 3.1: Configurable parameters

| Parameter     | Description                            |

|---------------|----------------------------------------|

| address_width | Bit width of matrix size (row, column) |

| data_width    | Bit width of pixel depth values        |

#### 3.1 Overall Design

The overall design of the Dense Optical Flow was broken into smaller parts called modules. These modules were designed to take on the same characteristics as the Matlab® commands. There are two different designs for the Reduce Matrix Function that will be developed in VHDL. These two designs will look at large area and small power consumption between the designs. These modules were built using VHDL and tested with test benches to prove that they functioned properly. Other Matlab® commands that will be created in VHDL are the following: Conv2, Round, Floor, Matrix Transpose, Compute Derivatives, Reduce Matrix Function, Adder, Multiplier, Divider, Subtractor, and Pinv. Also, the goal is to implement the Matlab® functions as VHDL modules. For instance, the 2×2 matrix called A has the following parameters while the 2×2 matrix called B has the following parameters:

Matrix A

$$\begin{pmatrix} 1 & 2 \\ 3 & 4 \end{pmatrix}$$

Matrix B  $\begin{pmatrix} 5 & 6 \\ 7 & 8 \end{pmatrix}$

The following Matlab® code calculates the two-dimensional convolution of Matrices A and B as seen in Equation 3.1. The resulting answer is stored in the  $3 \times 3$  Matrix C.

$$C = Conv2(A, B) \tag{3.1}$$

Matrix C produces the following result:

$$\text{Matrix C} \begin{pmatrix}

5 & 16 & 12 \\

22 & 60 & 40 \\

21 & 52 & 32

\end{pmatrix}$$

These results match the results from the VHDL convolution module with 0% error. The other Matlab® commands or functions were converted to VHDL to build the reusable module libraries to lay the foundation for Dense Optical Flow algorithm. The Matlab® commands that are only specific to Matlab® were developed and function properly include: Conv2, Matrix Transpose, Round, Floor, and Pinv.

#### 3.2 Two Dimensional Convolution

The two dimensional convolution Matlab® command Conv2 can be seen in Equation 3.1. The Conv2 to Matlab® command is the backbone for the image processing that has to take place in an application such as Optical Flow. Other Matlab® functions that were developed by Sohaib Khan, such as a Reduce Function and Computing Derivatives, can not be developed without the use of the Conv2 command. Therefore, the Conv2 command was the first module that was created.

Matrix C is created from the size of Matrix A and B. For example, Matrix C is [D+F-1, E+G-1]. These parameters come from the size of Matrix A[D,E] and Matrix B[F,G]. The algorithm for the Conv2 can be seen in Equation 3.2.

$$C(n_1, n_2) = \sum_{k_1 = -\infty}^{\infty} \sum_{k_2 = -\infty}^{\infty} a(k_1, k_2) b(n_1 - k_1, n_2 - k_2)$$

(3.2)

From the Matlab® Conv2 algorithm, VHDL modules were written and implemented having the same characteristics as the Matlab® command using a state

machine to take the place of the nested for-loops. The Conv2 Matlab® command requires the following modules to be built in VHDL in order for it to function:

- 1. Memory Module

- 2. Multiplier Module

- 3. Control Module

- 4. Multiplexer Module

- 5. Adder Module

- 6. Register Module

Once these modules are built, they will be connected together, like connecting Legos<sup>®</sup>together, to build the Conv2 Module for VHDL. Simulations will be run to test the VHDL Conv2 and the results will be compared to the Matlab<sup>®</sup> Conv2 command.

3.2.1 Memory. Picture images are made up of grayscale values between 0-255 integer values that makeup the brightness of the image. These values are used to discern between adjacent pixel colors of the images. A picture image is nothing more than a two-dimensional matrix that has rows and columns and is loaded with integer values to represent the brightness of the pixels. The memory method that will be used is to initially generate a matrix larger than the image that is going to have the Conv2 command performed on it. This is required when the Conv2 command is finished computing, the resultant matrix is larger than the initial image matrix size. Therefore, to take into account the matrix being larger than the initial image size, the memory module will initially be filled with all zero's. This oversized matrix eliminated the problem of the Conv2 command from stepping out of bounds when computing the results for the Conv2 command. The matrix can then be filled with the required grayscale values that represent the image.

3.2.2 Multiplier. The initial Multiplier Module that will be developed will only be a basic behavior model. The second Multiplier Module that will be developed

will be a 2-bit Booth Multiplier. This multiplier will be able to cut the clock cycle in half for calculating the results. For instance, the data input for the pixel value for the image is 8 bits, but we need to take into account the fractional parts of numbers that are multiplied together. The Matlab® Optical Flow uses a  $1 \times 5$  mask matrix that is made up of a Gaussian distribution. The Mask  $1 \times 5$  matrix has the following values:

Mask Matrix

$$\left( \begin{array}{cccc} .05 & .25 & .4 & .25 & .05 \end{array} \right)$$

When these calculations are performed, the results give a fractional part to the resultant. Therefore, we will use fixed-point notation to represent the fractional part of the number. In doing so, we will allocate 16 bits for the fractional part to represent the Gaussian distribution trying to minimize the error that will be caused since the values .05 or .4 will be only a close proximation of these values. This leaves us with 16 bits for the fraction part and 8 bits for the grayscale images yielding a total of 24 bits required to represent the images. We will initially set the image data width to 24 bits. However, this parameter is configurable to a larger bit width, if required.

- 3.2.3 Control. The Control Module could be implemented using a for-loop but these loops cannot typically be used for algorithmic iterations in synthesizable code [9]. Therefore, a state machine will be built to unroll the iterative loop that will increase throughput for the design.

- 3.2.4 Multiplexer, Adder, Register. The Multiplexer Module is used to switch between the loading of images and the Control Module, and is connected to the Memory Module. Once the image is loaded into the Memory, the Multiplexer will switch from a load mode to only communicate with the control logic. The Adder Module is used to add the values together once the multiplication is completed for a set of values. The Conv2 Matlab® commands require the sum of matrix positions to be multiplied and added together. The Register Module locks in the values that have been added together into its register. Once all the calculations have been completed,

the Control Module will send a signal to Matrix C so the data in the Register Module can be written into Matrix C at location (0,0).

#### 3.3 Matrix Transpose

Part of the Matlab® code transposes the input image. The following modules are required to build the Matrix Transpose Module:

- 1. Memory Module

- 2. Control Module

- 3. Multiplexer Module

Since the goal of the MSP is to create reusable libraries, creating the Matrix Transpose Module has been simplified because the Memory Module was already developed while creating the Conv2 command. Therefore, the only new module required to be built is a state machine Control Module to transpose a matrix.

# 3.4 Compute Derivatives

Another Matlab® function module that needs to be developed is one that is able to compute derivatives. The Fx and Fy derivatives are used to determine the edge detection of an object that has moved between Image1 and Image2. The Ft derivative is the summation of Image1 and Image2. You can picture it as placing Image2 on top of Image1, which forms the Ft derivative. The Compute Derivatives Module is built around the Matlab® Conv2 command. Again, the MSP reusable libraries make it possible for the creation of the Compute Derivative function by being able to recycle the Memory and Conv2 modules. The equation seen in Equation 3.3 is from the Compute Derivatives function that was written in Matlab® . This equation requires the Conv2 command to be used twice to multiply Image1 by a fixed  $2 \times 2$  matrix and added together with the result from Image2 being Conv2 with a fixed  $2 \times 2$  matrix.

$$Fx = Conv2(Image1, 0.25[-11; -11]) + Conv2(Image2, 0.25[-11; -11]);$$

(3.3)

The following modules are required to build the Compute Derivative Module:

- 1. Memory Module

- 2. Control Module

- 3. Conv2 Module

The Matlab® Compute Derivatives Function code can be seen in Listing III.2.

# Listing III.2:

```

1 [fx, fy, ft] = ComputeDerivatives(im1, im2);

3 function [fx, fy, ft] = ComputeDerivatives(im1, im2);

4 % ComputeDerivatives Compute horizontal, vertical and

5 % time derivative between two gray-level images.

6

7 if (size(im1,1) ~= size(im2,1)) | (size(im1,2) ~= size(im2,2))

error('input images are not the same size');

9

end;

10

11 if (size(im1,3)~=1) | (size(im2,3)~=1)

error('method only works for gray-level images');

13 end;

14

15

16 fx = conv2(im1, 0.25*[-1 1; -1 1]) + conv2(im2, 0.25*[-1 1; -1 1]);

| 17 | fy = conv2(im1, 0.25*[-1 -1; 1 1]) + conv2(im2, 0.25*[-1 -1; 1 1]);

18 ft = conv2(im1, 0.25*ones(2))+conv2(im2, -0.25*ones(2));

19

20 % make same size as input

21 fx=fx(1:size(fx,1)-1, 1:size(fx,2)-1);

22 fy=fy(1:size(fy,1)-1, 1:size(fy,2)-1);

23 ft=ft(1:size(ft,1)-1, 1:size(ft,2)-1);

```

# 3.5 Reduce Matrix Function

When dealing with image processing, the images need to be down sampled in size. This down sampling is part of the Optical Flow. We will use the terminology Reduce Matrix Function instead of down sampling. The Reduce Matrix Function is another Matlab® function that needs to be created in VHDL. The Reduce Matrix Function Module takes the initial image and reduces it in size by one half. For example, an initial image size of  $250 \times 400$  will be  $125 \times 200$  after performing the Reduce Matrix Function. Here is another example of how the MSP design thought process uses the created reusable libraries to develop another module. The key module in image processing is the Conv2 Module; again, it is used to build another module. The following modules are required to build the Reduce Matrix Function Module:

- 1. Conv2 Module

- 2. Control Module

- 3. Reduce Control Horizonal Module

- 4. Reduce Control Vertical Module

- 5. Memory Module

- 6. Multiplexer Module

- 7. Adder Module

- 8. Register Module

The Matlab® Reduce Matrix Function code can been seen in Listing III.3.

# Listing III.3:

```

7 % Gaussian mask = [0.05 0.25 0.4 0.25 0.05]

8 % Apply 1d mask to alternate pixels along each row of image

9 % apply 1d mask to each pixel along alternate columns

10 % of resulting image

11

12 \text{ mask} = [0.05 \ 0.25 \ 0.4 \ 0.25 \ 0.05];

13

14 hResult = conv2(im, mask);

15 hResult = hResult(:,3:size(hResult,2)-2);

16 hResult = hResult(:, 1:2:size(hResult,2));

17

18 vResult = conv2(hResult, mask');

19 vResult = vResult(3:size(vResult,1)-2, :);

20 vResult = vResult(1:2:size(vResult,1),:);

21

22 smallIm = vResult;

```

#### 3.6 Round/Floor

The Round and Floor commands are predefined Matlab® commands that do not exist in VHDL. The Round Module will take an input and round it up or down depending on what the fractional part of the number is. If, for example, the number is 4.5, the Round Module will round the number to 5 and if the number is 4.49 it will round the number to 4. On the other hand, the Floor command will take the floor of a number. For example, if the value is 5.9 it will floor the value to 5.

#### 3.7 Pseudoinverse (Pinv)

The Pseudoinverse, also known as Pinv, is used to calculate the inverse of a matrix. Not all matrices have an inverse, therefore, the Pseudoinverse is used to find a close matrix inverse for a matrix. The Pseudoinverse [12] Equation 3.4 is the equation used to calculate the Pseudoinverse for Matrix A and the answer is stored in Y. The Matlab® code uses the equation seen in Equation 3.5 to do this

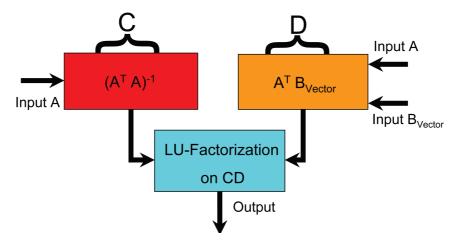

calculation. The method used to build the Pseudoinverse Module will be to use the Matrix Transpose module and multiply it by the original Matrix A. While that is being done, we will multiply Matrix Transpose by  $B_{Vector}$ , where the  $B_{Vector}$  is the Ft derivative. Doing these two multiplications in parallel, we will perform the matrix inverse on the resultants using the LU-Factorization method [6] to find the inverse. The Pseudoinverse Module will include the following modules for its development:

$$Y = (A^T A)^{-1} A^T (3.4)$$

$$Y = (A^{T}A)^{-1}(A^{T}B_{Vector}) (3.5)$$

- 1. Memory Module

- 2. Control Module

- 3. Multiplier Module

- 4. Divider Module

- 5. Adder Module

- 6. Matrix Transpose Module

- 7. Register Module

#### 3.8 Synthesis/Timing

The Xilinx®Virtex-4 SX ML402 FPGA will be the target FPGA to attain the power, area, and delay of the circuits. The Virtex-4 is a generalized moderate cost FPGA that is a practical standard FPGA for DSP applications. The Virtex-4 ML402 is a good evaluation board with a wide range of applications such as DSP and low power. The Precision RTL®RTL 2007a.8 and Xilinx®ISE 9.2 are the two synthesis tools that will be used.

In one method, the two dimensional convolution module is built using sequential and combinational modules that make up the Conv2. The Conv2 module does many

multiplications and additions to compute the result for Matrix C. These sub-modules are built using combinational logic. Therefore, if the clock runs too fast, the multiplications and additions will not be completed before the next clock cycle, causing the wrong result to be stored in Matrix C. One of the ways to eliminate this problem is to lower the clock speed.

A second method would be to place a pipeline register between the multiplier and adder to increase throughput by increasing the clock speed. Timing is important for Dense Optical Flow due to the number of calculations required to complete two simple  $2 \times 2$  matrices to create a  $3 \times 3$  matrix. Timing simulations will show how fast the system can run to increase throughput. Timing simulations can also determine if it is required to add additional pipeline registers to increase throughput. The timing simulations can also determine how slow the clock can run without including additional registers or hardware. By slowing the clock speed to a minimal speed, power can be saved in the design. All these things rely on the timing simulations. The Mentor Graphics®tools will also play a role in attaining the results for Chapter 4 of this thesis project.

#### 3.9 Testing Procedure

There are several ways to perform testing on these modules that will be developed. First, Modelsim®version 6.3c will be used to develop the VHDL code. The Modelsim®software will also be used to generate test benches to show the functionality of modules. Once the VHDL modules are functioning, they will be run through the Precision RTL®2007a.8 and Xilinx®ISE 9.2 software programs for synthesis to look at power, area, and delay of the circuits. This will give an estimate of how to reduce high power draws that occur due to the high amounts of calculations required by Dense Optical Flow. This may require that the circuit clock speeds be slowed down to reduce power, which in turn can minimize circuit size and slow the speeds of the system being tested.

# 3.10 Chapter Summary

The idea of breaking the Matlab® commands and functions into synthesizable reusable library modules that are used in image processing were discussed. These modules will support AFRL/RY later when they want to create the Optical Flow as a system by taking the synthesizable reusable libraries and connecting them together to build an Optical Flow that can be fully designed in VHDL. The synthesis, timing, and testing procedures were introduced and discussed. The software that will be used to carry out this methodology was discussed and how it will be used. Each submodule was thoroughly tested to ensure there will be no errors when final assembly of the sub-modules are connected to create an MSP module such as a Conv2, Matrix Transpose, Round, Floor, and Pinv, etc.

# IV. Analysis and Results

This chapter will discuss the overview design of the MSP modules that were discussed in the methodology section. We will also look at the power, area, and delay for the MSP modules. We will also look at the error analysis calculated between the Matlab® code and the VHDL modules.

#### 4.1 Overview of MSP Modules

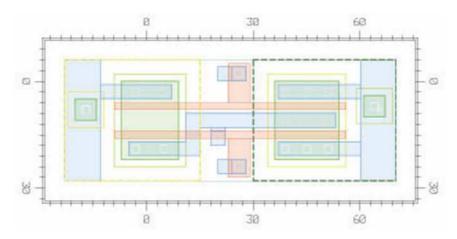

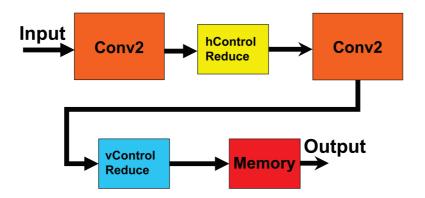

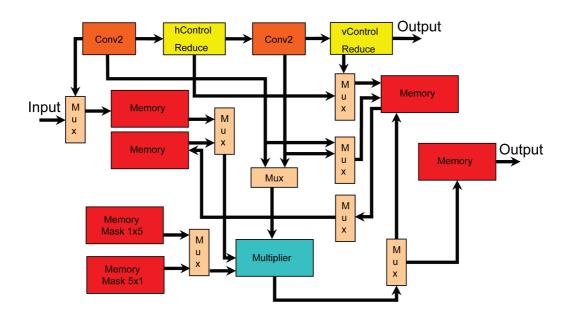

The overarching module that needed to be created was the Conv2 Module. This module was used in the development of the Reduce Matrix Function and Computing Derivatives. The Top-Level Design 1 for the Reduce Matrix Function can be seen in Figure 4.1. The Reduce Matrix Function requires the use of Conv2 Module to perform the Conv2 Matlab® command. When using the Conv2 command in Matlab® the matrix size grows larger due to the Conv2 algorithm. The hControl/vControl Reduce Module are used to reduce the oversized matrix that is created when Conv2 is performed. The Reduce Matrix Function is used to reduce a matrix size in half. For example, an image the size of  $6 \times 8$  reduces to a  $3 \times 4$ . The Conv2 Module will generate a  $6 \times 12$  matrix down to  $6 \times 4$ . The Conv2 Module will generate a  $10 \times 4$  which will be reduced to  $3 \times 4$  using the vControl Reduce Module. The final image is stored in the Memory Module as a  $3 \times 4$ .

Figure 4.1: Reduce Matrix Function Top Level Design 1

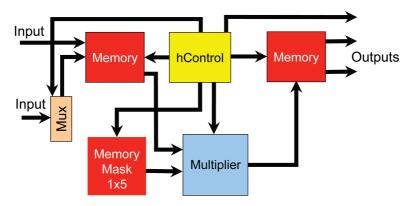

Figure 4.2: Conv2 Sub-Modules Design

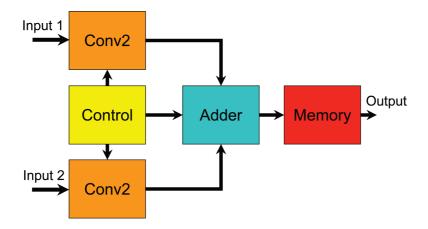

The modules that were used in the the Top-Level Design 1 for the Conv2 Module can be seen in Figure 4.2. These modules make up the Conv2 Module. The first Conv2 Module uses a  $1 \times 5$  Mask matrix opposed to the  $5 \times 1$  Mask matrix that is used in the second Conv2 Module. The Conv2 Module design uses Multiplexer, Memory, Multiplier and Controller Modules. They are connected together to achieve the result for Conv2 Matlab® command.

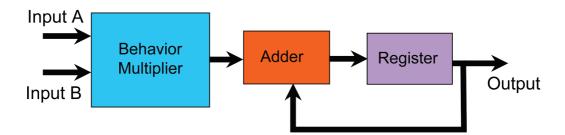

The Behavior Multiplier can be seen in Figure 4.3. The three modules, Behavior Multiplier, Adder, and Register are required in the development of the Conv2 command.

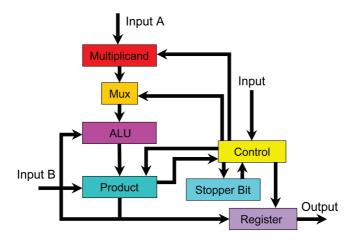

The modules that are required to build a 2-bit Booth Multiplier Module can be seen in Figure 4.4. The Booth Multiplier Module requires the input values to be loaded into the Multiplicand and Product Module. The Control Module is used to communicate between the other modules.

Figure 4.3: Behavior Multiplier Module Design

Figure 4.4: Booth Multiplier Module Design

The Top-Level Design 2 that was used to develop the Reduce Matrix Function can be seen in Figure 4.5. This design approach eliminates the use of a second Multiplier Module reducing power consumption and minimizing area compared to Top-Level Design 1. Further analysis will be discussed later in Chapter 4 to see the differences between the two design methods. Every large scale design requires a Control Module to communicate between the other modules. The Control Module is basically the "brains" for the module.

Figure 4.5: Reduce Matrix Function Top Level Design 2

Figure 4.6: Multiplier State Machine Design

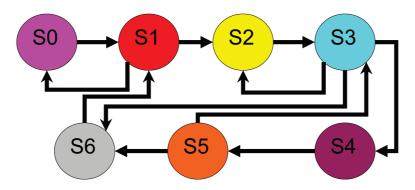

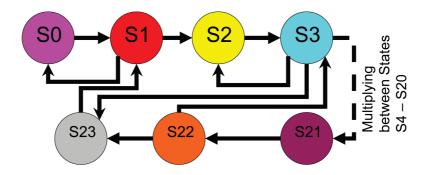

The Control Module that was used for the Behavior Multiplier Module uses seven states for its state machine. The Control Module is used to communicate between the Multiplier Module and the other modules. The seven states that the Control Module uses to communicate with the Behavior Multiplier Module can be seen in Figure 4.6. The Booth Multiplier, on the other hand, requires that the Control Module be built using 24 states for its state machine if using a 32 bit input. The Booth Multiplier state machine can be seen in Figure 4.7. The Booth Multiplier is performing its shifts, adds, and subtraction operations during States S4-S20 for a 32 bit number. If the input number was to be reduced to 24 bits, it would require 4 less states for the Controller to use.

The Compute Derivatives Top-Level Design can be seen in Figure 4.8. Again, you can see how the Conv2 Module was used to build the Compute Derivatives Module. This function requires the use of the Conv2, Controller, Adder, and a Memory

Figure 4.7: Booth Multiplier State Machine Design

Figure 4.8: Compute Derivatives Top-Level Design

to build the derivative module in VHDL. The MSP Design effort payed off in the creation of the MSP Compute Derivatives Modules by being able to reuse previously designed modules.

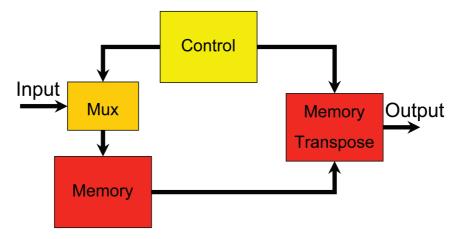

The Matrix Transpose Module requires the use of a Multiplexer, Controller, and Memory. The Matrix Transpose Module receives data through the Multiplexer which loads the Memory. The Controller is used to transpose the values from the Memory to Memory Transpose. The Top-Level design of the Matrix Transpose Module can be seen in Figure 4.9.

Figure 4.9: Matrix Transpose Top-Level Design

Figure 4.10: Pseudoinverse Top-Level Design

The Pseudoinverse (Pinv) Module can be broken into 3 Modules. The  $(A^TA)^{-1}$  is one module, the  $A^TB_{Vector}$  the other module, and finally the module that will perform the LU-Factorization. The Pinv Module Top-Level Design can be seen Figure 4.10.

# 4.2 Error Analysis

When creating the VHDL modules to have the same functionality as the Matlab® commands and functions, error is introduced. Part of this error is introduced and can be seen from the Mask Matrix  $1 \times 5$  or its transpose  $5 \times 1$  that have the Gaussian Distributions values in the Memory Matrix. The values .05 and .40 can not exactly be represented in binary numbers when only using a limited amount of bits to represent these values. We used 16 bits to represent the fractional part of the Mask Matrix values. Therefore, when the Conv2 Module multiplies the image by the mask, the resultant will have error. This is due to the fact that the Mask Values were not being exactly compared to the Matlab® values. The close approximation values that were used for the Mask Matrix and Matlab® values can be seen in Table 4.1. The error analysis equation that will be used is  $\%Error = \frac{VHDL-MATLAB}{MATLAB} \times 100$ .

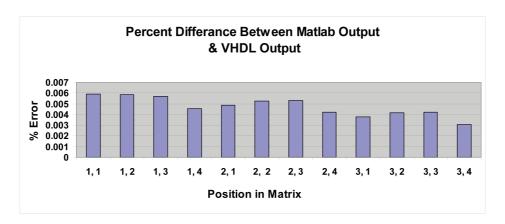

The error analysis that was shown for the Reduce Matrix Function for the VHDL compared to the Matlab® can be seen in Figure 4.11. The largest amount of error

Figure 4.11: Reduce Matrix Function Matlab® vs. VHDL Percent Error

Table 4.1: Comparison between Matlab® and VHDL Gaussian Distribution

| Matlab <sup>®</sup> Gaussian Distribution | 0.05        | 0.25 | 0.4         | 0.25 | 0.05        |

|-------------------------------------------|-------------|------|-------------|------|-------------|

| VHDL Gaussian Distribution                | 0.049987793 | 0.25 | 0.399993896 | 0.25 | 0.049987793 |

| % Error Difference                        | 0.024414    | 0    | 0.001526    | 0    | 0.024414    |

that occurred was .0059% for the sample  $6 \times 8$  data set that we used. The  $6 \times 8$  data set that was used can be seen in the Input Data Matrix. This data set was arbitrarily chosen. The Reduce Matrix Function reduces the  $6 \times 8$  matrix down to  $3 \times 4$ , but not before the  $6 \times 8$  has the Conv2 Module performed on it. The x-axis represents the positions in the the  $3 \times 4$  matrix. The y-axis shows the percent error between the Matlab® output and the VHDL output.

The Compute Derivatives for Fx, Fy, and Ft had zero percent error compared to the Matlab® code. This is due to the fact that the Compute Derivative equation

used a positive or negative  $2 \times 2$  matrix with the values .25 which can be represented in binary with zero percent error. Also, the Matrix Transpose Module had zero error because it took the original Matrix A and transposed it to become Matrix A<sup>T</sup>. There was no loss of data precision when transposing Matrix A.

The sample test data set that was used to test the Pseudoinverse Module was Matrix A  $9 \times 2$  and Matrix  $B_{Vector}$   $9 \times 1$ . The comparison between Matlab® and VHDL results can be seen in Table 4.2. The results are stored in a  $2 \times 1$  matrix. The largest percent error from the sample test data was 2.65%. A small amount of error occurs from the divider that is used to calculate the Pseudoinverse. This small error gets magnified when the value is multiplied. This intermediate result is divided and multiplied again as part of the LU-Factorization in order to find the Pseudoinverse.

Table 4.2: Comparison between Matlab® and VHDL Pseudoinverse Module

|                    | Matrix Position (1, 1) | Matrix Position (2, 1) |

|--------------------|------------------------|------------------------|

| Matlab® Results    | 0.731775               | 0.305488               |

| VHDL Results       | 0.716705               | 0.313827               |

| % Error Difference | 2.10                   | 2.65                   |

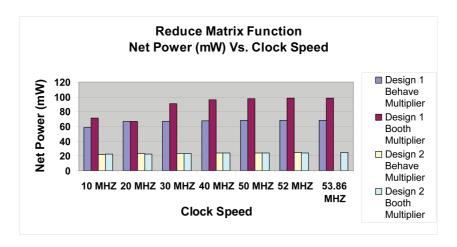

Figure 4.12: Reduce Matrix Function Module Net Power(mW) vs. Clock Speed

#### 4.3 Power, Area, and Delay

In the power, area, and delay section we will look at the results that were attained from the MSP modules implemented using the Cadence®synthesis tool. The Cadence®software tool did not specifically target an FPGA or an ASIC for the results that were attained.

First, we will look at the results that were attained from the Reduce Matrix Function, seen in Figure 4.12. From the excel chart, it is clear that the Top-Level Design 2 approach requires less net power to be used for the Reduce Matrix Function Module. The power savings that occurs for Top-Level Design 2 over Top-Level Design 1 is at least 2.8 times smaller. In Figure 4.12 the Cadence®software also stated that the fastest delay for Top-Level Design 1 using a behavior Multiplier Module ran at 52.02 MHz. The other designs ran at 53.86 MHz.

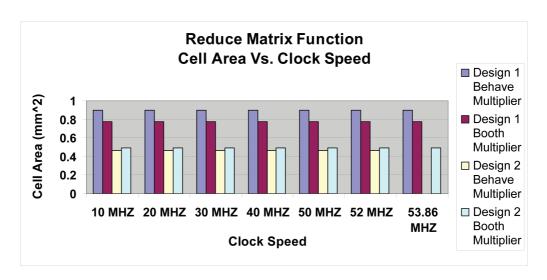

In Figure 4.13 it is clear that Top Level Design 2 uses a smaller area in the design, up to 54.6% smaller, compared to the Behavior Multiplier Top-Level Design 1 and Booth Multiplier Top-Level Design 2.

The results for Fx, Fy, and Ft can be seen in Figure 4.14 for Power vs. Clock Speed using the Cadence®software. As expected, as you increase the clock speed, the net power increases. The clock speeds and area that were attained for the excel charts

Figure 4.13: Reduce Matrix Function Module Cell Area vs. Clock Speed

Figure 4.14: Compute Derivatives Module Net Power(mW) vs. Clock Speed

Figure 4.15: Compute Derivatives Module Cell Area vs. Clock Speed

are only estimations generated from the Cadence®software. Every software package uses different algorithms to attain the power, area, and delay.

The area for the Compute Derivatives was unchanged as the speed increases as shown in Figure 4.15. For example, you are able to achieve the same cell area for 10 MHz design or a 52 MHz design.

The Matrix Transpose Module achieved the results for Power vs. Clock Speed in Figure 4.16. The net power increased as the speed increased which is what is

Figure 4.16: Matrix Transpose Module Net Power(mW) vs. Clock Speed

Figure 4.17: Matrix Transpose Module Cell Area vs. Clock Speed

expected. The cell area was unchanged when the clock speed was increased. This can be seen in Figure 4.17.